# 262,144-BIT DUAL PORT DYNAMIC RANDOM ACCESS MEMORY

#### 262,144 Bit Dual Port DRAM

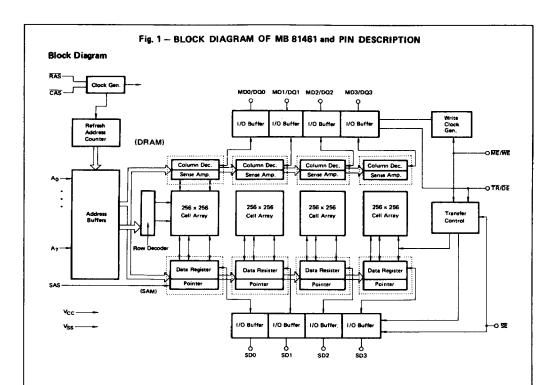

The Fujitsu MB81461 is a fully decoded, dynamic NMOS random access memory organized as 65,536 words by 4 bits dynamic RAM port and 256 words by 4 bits serial access memory (SAM) port.

The DRAM port is identical to the Fujitsu MB81464 with four bits of parallel random access I/O while the SAM port is designed as four 256-bit registers, each operating as a serial I/O. The four serial registers operate in parallel with each other during SAM port operation. Internal interconnects give the device the capability to transfer data bi-directionally between the DRAM memory array and the SAM data registers.

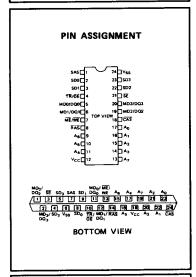

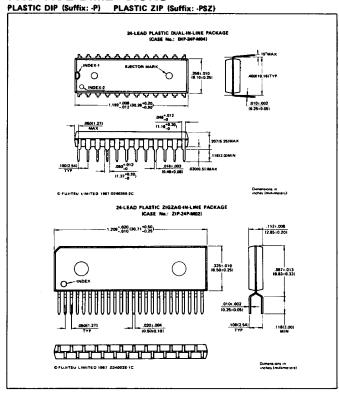

The MB81461 offers complementary asynchronous access of both the DRAM and SAM ports, except when data is transferred between them internally. The design is optimized for high speed and performance making the MB81461 the most solution for implementing the frame buffer of a bit-mapped video display system. Multiplexed row and column address inputs permit the MB81461 to be housed in a 400-mil wide 24-pin DIP or ZIP package. Pinouts conform to the JEDEC-approved pinouts.

The MB81461 is fabricated using silicon gate NMOS and Fujitsu's advanced Triple-layer Polysilicon process technology. This process, coupled with single transistor memory storage cells, permits maximum circuit density and minimum chip size. All inputs and outputs are TTL compatible.

- Dual Port Organization

64 K x 4 Dynamic RAM port (DRAM)

256 x 4 Serial Access Memory port (SAM)

- SAM)

24-pin DIP and ZIP packages

- Silicon-gate, Triple Poly NMOS, single transistor cell

- DRAM Port

Access Time (trac)

120 ns max. (MB 81461-12)

150 ns max. (MB 81461-15)

Cycle Time (tsac) 230 ns max. (MB 81461-12) 260 ns max. (MB 81461-15)

SAM Port

Access Time (ts.c.)

40 ns max. (MB 81461-12)

60 ns max. (MB 81461-15)

Cycle Time (ts.c.)

40 ns max. (MB 81461-12)

60 ns max. (MB 81461-15)

- Single +5 V Supply, ±10% tolerance

- · Real Time, Read Transfer capability

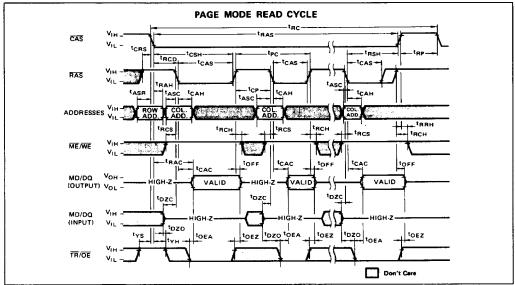

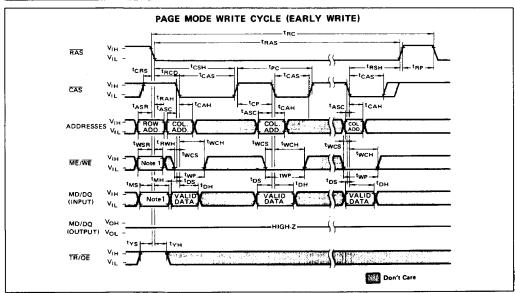

- Page Mode capability

- Power Dissipation

DRAM, Act/SAM; Stby

523 mW max. (MB 81461-12)

468 mW max. (MB 81461-15)

DRAM; Stby/SAM; Act

275 mW max. (MB 81461-12)

220 mW max. (MB 81461-15)

DRAM; Stby/SAM; Stby

110 mW max.

- Bi-directional data transfer between DRAM and SAM

- Fast serial access asynchronous to DRAM except transfer operation

- Bit Masked Write Mode capability

- 256 refresh cycles every 4 ms

- RAS-only, CAS-before-RAS, Hidden Refresh capability

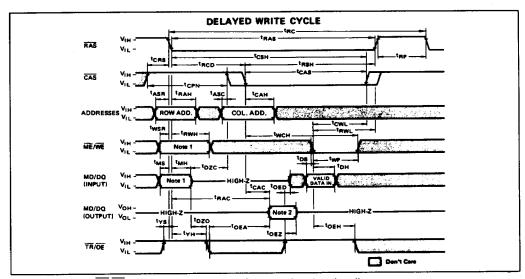

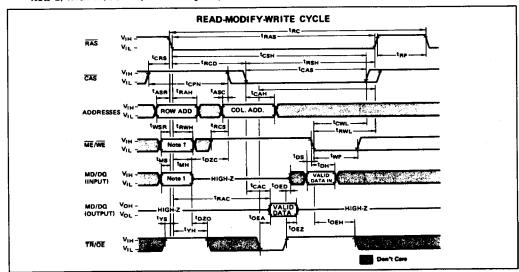

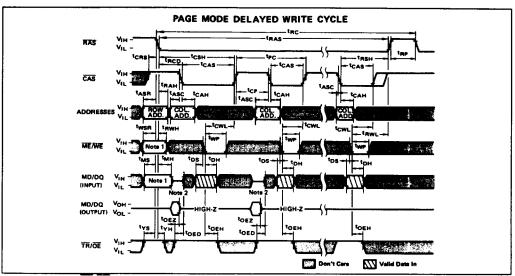

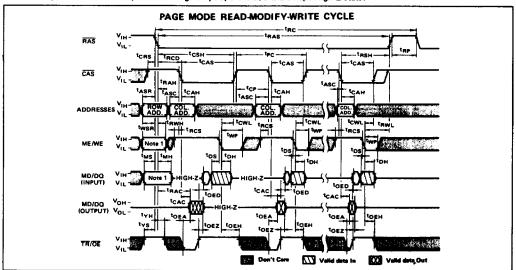

- Delayed write and Read-Modify-Write capability

- Standard 24-Pin Plastic Packages: DIP (MB81461-XXP) ZIP (MB81461-XXPSZ)

#### Absolute Maximum Ratings (See Note)

| Parameter                                                     | Symbol                            | Value       | Unit |

|---------------------------------------------------------------|-----------------------------------|-------------|------|

| Voltage at any pin relative to V <sub>SS</sub>                | V <sub>IN,</sub> V <sub>OUT</sub> | -1 to +7    | ٧    |

| Voltage of V <sub>CC</sub> supply relative to V <sub>SS</sub> | Vcc                               | -1 to +7    | ٧    |

| Storage Temperature                                           | TSTG                              | -55 to +125 | °င   |

| Power Dissipation                                             | PD                                | 1.0         | w    |

| Short Circuit Output Current                                  |                                   | 50          | mA   |

Note: Permanent device damage may occur if absolute maximum ratings are exceeded.

Functional operation should be restricted to the conditions as detailed in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

PLASTIC PACKAGE

DIP-24P-M04

PLASTIC PACKAGE

ZIP-24P-M02

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to evoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Copyright © 1990 by FUJITSU LIMITED and Fujitsu Microelectronics, Inc.

#### Pin Description

| Pin N                             | umber                           | 0                                |                                   |              |

|-----------------------------------|---------------------------------|----------------------------------|-----------------------------------|--------------|

| DIP                               | ZIP                             | Symbol                           | Parameter                         | Mode         |

| 1                                 | 7                               | SAS                              | Serial Access Memory Strobe       | Input        |

| 2,3,22,23                         | 8,9,4,5                         | SD0 to SD3                       | Serial Data I/O                   | 1/0          |

| 4                                 | 10                              | TR/OE                            | Transfer Enable/<br>Output Enable | Input        |

| 5,6,19,20                         | 11,12,1,2                       | MD0/DQ0<br>to<br>MD3/DQ3         | Mask Data/Data I/O                | 1/0          |

| 7                                 | 13                              | MÉ/WE                            | Mask Mode Enable/Write Enable     | Input        |

| 8                                 | 14                              | RAS                              | Row Address Strobe                | Input        |

| 17, 16, 15<br>14, 11, 10<br>9, 13 | 23,22,21,<br>20,17,16,<br>15,19 | A <sub>0</sub> to A <sub>7</sub> | Address Input                     | Input        |

| 12                                | 18                              | Vcc                              | Supply Voltage +5 V               | Power Supply |

| 18                                | 24                              | CAS                              | Column Address Strabe             | Input        |

| 21                                | 3                               | SE                               | Serial port Enable                | Input        |

| 24                                | 6                               | V <sub>SS</sub>                  | Ground                            | Power Supply |

### DESCRIPTION

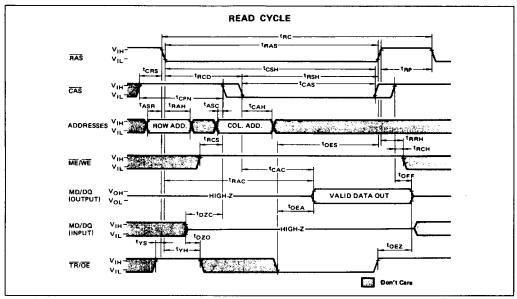

#### DRAM OPERATION

#### RAS:

This pin is used to strobe eight row-address inputs from A0 to A7 pins and is used to select the operation mode of subsequent cycle, such as DRAM operation or transfer operation (by  $\overline{TR}/\overline{OE}$  and bit mask write cycle or not (by  $\overline{ME}/\overline{WE}$  and MD0/DQ0 to MD3/DQ3). Since  $\overline{RAS} = "L"$  is the active condition of circuit, to maintain  $\overline{RAS} = "H"$  (standby condition) is effective to save power dissipation.

#### CAS:

This pin is used to strobe eight column address inputs at the falling edge. CAS pin has the function to enable and disable the output at "L" and "H" respectively during the read operation.

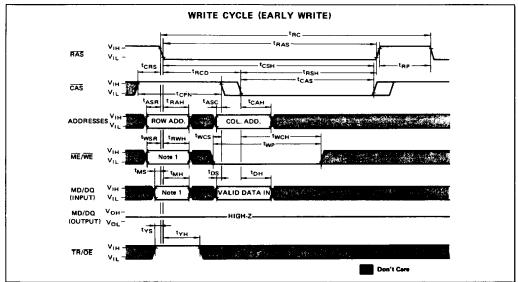

Another function of  $\overline{CAS}$  is to select "early write" mode conditioned by  $\overline{ME}/\overline{WE} = "L"$

#### ME/WE:

This pin is used to select read or write cycle. ME/WE = "L" select write mode and ME/WE = "H" select read mode. This pin is also used to enable bit mask write cycle. If ME/WE = "L" at the falling edge of RAS, bit mask write is enabled.

#### TR/OE:

This pin is used to select Transfer operation or not at the falling edge of RAS, TR/OE = "H" enables DRAM operation and TR/OE = "L" enables Transfer operation between DRAM and SAM. After the falling of RAS with  $t_{YH}$ , this pin is used for output enable.

The TR/OE controls the impedance of the output buffers. TR/OE = "H" forces the output buffers at high impedance state. TR/OE = "L" leads the output buffers at low impedance state. But in early write cycle, the output buffers are high impedance state even if TR/OE is low.

#### A0 to A7;

These are multiplexed address input

pins and used to select 4 bits of 262,144 memory cell locations in parallel within the MB 81461. The eight row address inputs are strobed by RAS and followed eight column address inputs are strobed by CAS. These are used to select the start address of serial access memory also.

#### MD0/DQ0 to MD3/DQ3

These are common I/O pins of DRAM port. I/O mode is as specified for each function mode in the truth table.

#### **Data Outputs:**

The output buffers have three-state capability "H", "L" and "High-Z". To get valid output data on the pins, one of the read operations is selected such as "read" or "read-modify-write" mode. During a refresh cycle, either RAS-only or CAS-before-RAS mode is selected, output buffers are set in "High-Z" state.

#### Data inputs:

These are used as data input pins when a data write mode such as "Early-Write", "Delayed Write" or "Read-modify-Write" is selected. In any of the above cases, these pins are set at "High-Z" state to enable data-in without any bus conflict.

In any operation mode, read, write, refresh, transfer and their combined functions, output states "H", "L", "High-Z" are set by control signals RAS, CAS, ME/WE and/or TR/OE. When "Bit mask write" mode is set, these pins are used as a control signal for write inhibit with MDi/DQi = "L" on the selected bit i.

#### Page Mode;

The page mode operation is to strobe the column address by CAS while RAS is maintained at "L" through all the successive memory operations if the row address doesn't change. This mode can save power dissipation and get the faster access time due to the elimination of RAS falling edge function.

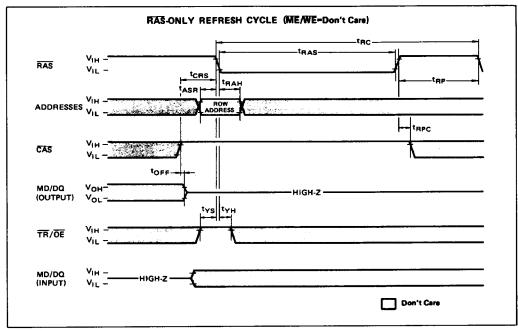

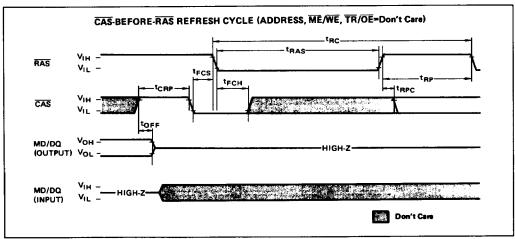

#### Refresh:

Refresh of the DRAM cells is performed for every 256 rows per every 4 milliseconds.

The MB 81461 offers the following three types of refresh.

- 1) RAS-Only refresh; The RAS-Only refresh is performed with CAS="H" condition. Strobing every 256 row addresses with RAS will complete all bits of memory cell to be refreshed while all outputs are invalid due to "High-Z" state. Further RAS-only refresh saves the power dissipation substantially.

- 2) CAS-before-RAS refresh; The CAS-before-RAS refresh offers an alternate refresh method. If CAS is set low for the specified period (t<sub>FCS</sub>) before the falling edge of RAS, refresh control clock generator and refresh address counter are enabled, and an refresh operation is performed. After the refresh operation is performed, the refresh address counter is incremented automatically for the next CAS-before-RAS refresh.

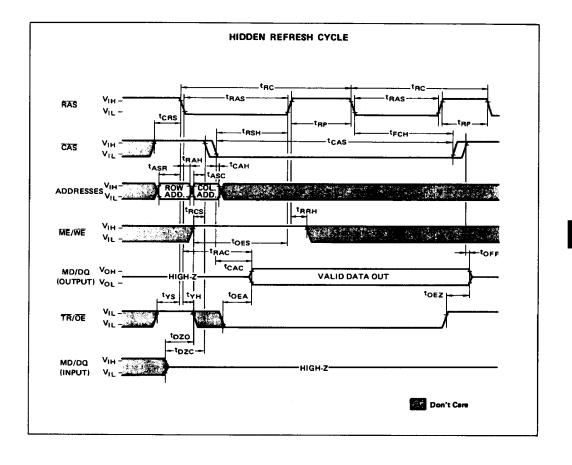

- 3) Hidden refresh; The hidden refresh is performed by maintaining the valid data of last read cycle at MD/DQ pins while extending CAS low. The hidden refresh is equivalent to CAS-before-RAS refresh because CAS stays low when RAS goes to low in the next cycle.

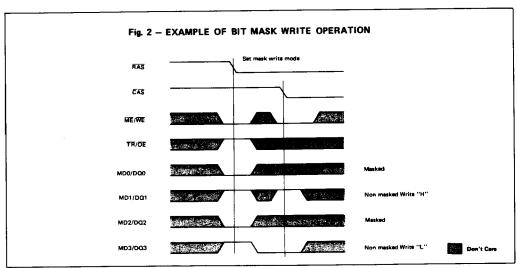

#### Bit Mask Write;

This mode is used when some of the bits should be inhibited to be written into cells. The bit mask write mode is executed by setting ME/WE = "L" at the falling edge of RAS during write mode (early, delayed write or read-modify-write cycle). The bits to be masked (or inhibited to write) is determined by MD/DQ state at the falling edge of RAS, for example, if MD0/DQ0 and ME/WE are both low at the falling edge of RAS, the data on MD0/DQ0 pin is not written into the cell during the cycle. Refer to the Fig. 2.

# EXAMPLE OF BIT MASK WRITE OPERATION

|       |       | Function |         |            |         |                                                               |

|-------|-------|----------|---------|------------|---------|---------------------------------------------------------------|

| TR/OE | ME/WE | MD0/DQ0  | MD1/DQ1 | MD2/DQ2    | MD3/DQ3 |                                                               |

|       | Н Н   | ×        | ×       | х          | ×       | Write enable                                                  |

| н     |       | н        | L       | н          | L       | Write enable for DQ0 and DQ2<br>Write disable for DQ1 and DQ3 |

|       |       |          | L       | l. —. —. · | 1       | X: Don't Care                                                 |

### FUNCTIONAL TRUTH TABLE FOR DRAM OPERATION

| UNCTION        | AL TRUTH    | TABLE FOR | DRAM OPER                       | ATION       |                                   |                        |

|----------------|-------------|-----------|---------------------------------|-------------|-----------------------------------|------------------------|

| RAS            | CAS         | ME/WE     | TŘ/OE                           | ADDRESSES   | MD0/DQ0 to<br>MD3/DQ3             | Function               |

| H              | Н           | ×         | ×                               | х           | X                                 | Standby                |

|                |             | Н         | H→L                             | Valid       | Valid Data Out                    | Read                   |

|                | <del></del> | 1.*       | H→X                             | Valid       | Valid Data In                     | Early Write            |

| <del>-</del> - |             | H→L       | $H \rightarrow X \rightarrow H$ | Valid       | Valid Data In                     | Delayed Write          |

| <u>L</u>       | L           | H→L       | H→L→H                           | Valid       | Valid Data Out<br>→ Valid Data In | Read-Modify-Write      |

|                | Н           | x         | H→X                             | Row address | High-Z                            | RAS-Only Refresh       |

| H→L            | L           | X         | н→х                             | ×           | High-Z                            | CAS-before-RAS Refresh |

\*: If ME/WE = "L" at the falling edge of RAS, bit mask write mode is enabled.

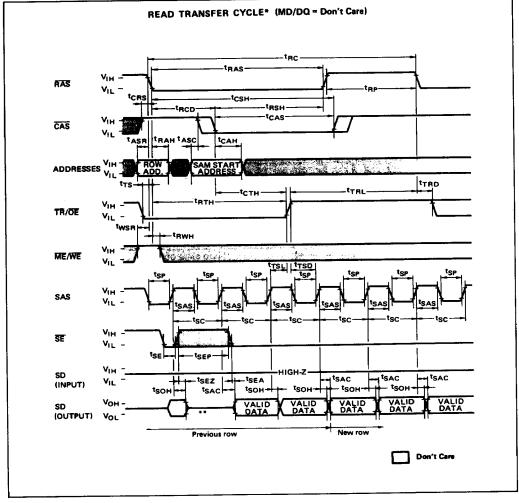

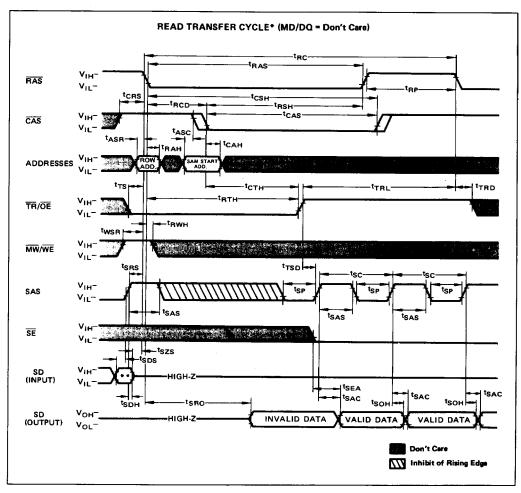

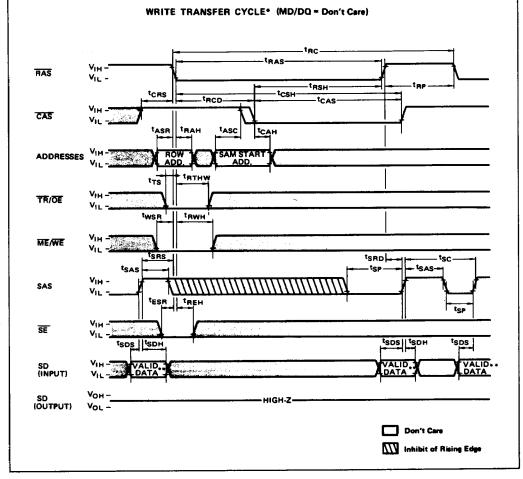

#### TRANSFER OPERATION:

The transfer operation is featured in the MB 81461B. This mode is used to transfer simultaneously 256x4 data from DRAM to SAM or from SAM to DRAM. The direction of transfer is determined by the state of ME/WE at the falling edge of RAS. ME/WE="H" defines the transfer from DRAM to SAM (Read Transfer Cycle) and ME/WE="L" defines the transfer from SAM to DRAM (Write Transfer Cycle).

1/O mode of SD0 to SD3 determined while the transfer operation is set (TR/ OE="L") conjunctioned with ME/WE

After Read Transfer Cycle, please apply two or more SAS Clock.

This pin is used to enable transfer oper ation at the falling edge of RAS.

#### ME/WE:

This pin is used to select the direction of transfer at the falling edge of RAS. A0 to A7;

These pins are used to select the row address of DRAM port to be transfered from or to, and the start address of SAM port for the serial read or write operation. The row address is strobed by RAS and the start address is strobed by CAS.

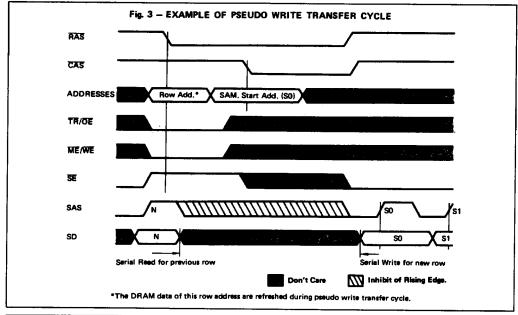

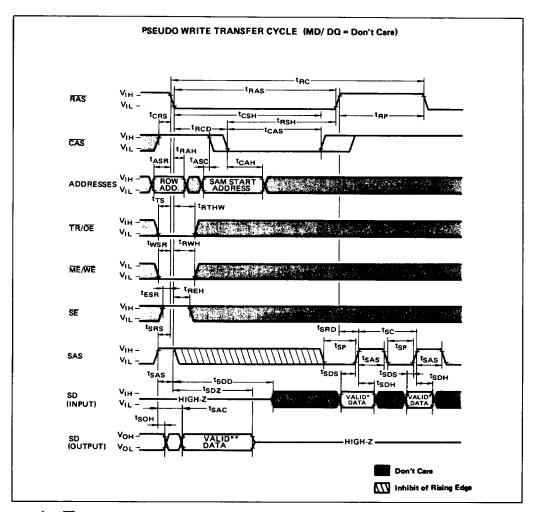

#### Pseudo Write Transfer:

To start serial write cycle, the SD pins must be set in input mode. To do this, write transfer cycle should be executed. The pseudo write transfer cycle is to change the SD pins into input mode without data transfer from SAM to DRAM. Refer to Fig. 3.

#### Refresh during transfer cycle;

DRAM and SAM are refreshed during transfer cycle as shown below.

- 1) Read transfer cycle:

- During read transfer cycle, the selected row address of DRAM to be transfered to SAM is refreshed. SAM data are kept by applying 256 SAS clocks within 4 ms after the read transfer cycle.

- 2) Write transfer cycle:

During write transfer cycle, the new data are written from SAM to DRAM and this row address should be refreshed within 4 ms.

But SAM data are not refreshed during write transfer cycle. Therefore, the SAM refresh (applying 256 SAS clocks within 4 ms) must be executed. Especially, when the write transfer cycle is executed continuously, 256 SAS clock should be applied within 4 ms.

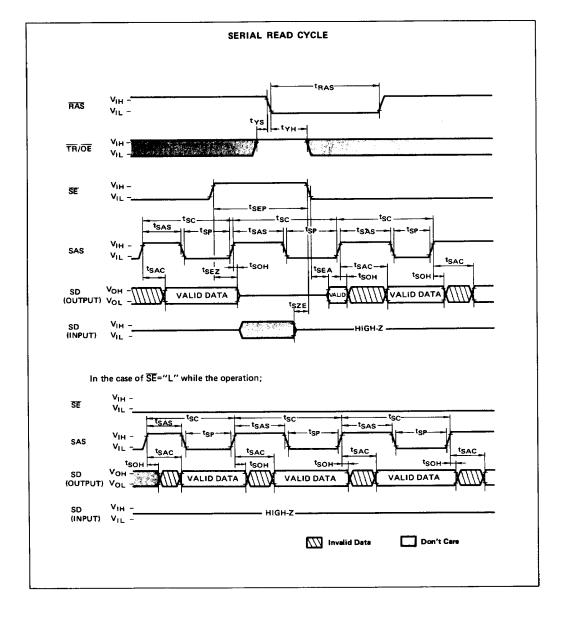

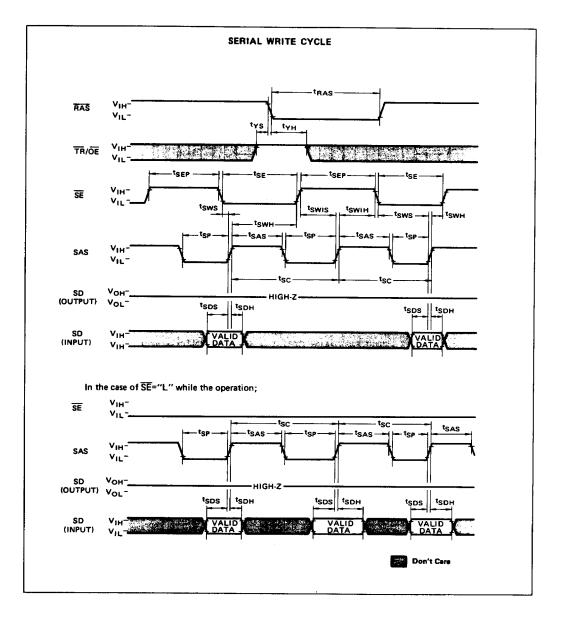

#### SERIAL ACCESS OPERATION:

The MB 81461 has 256 words by 4 bits Serial Acess Memory (SAM) corresponding to 64K words by 4 bits DRAM and the fast serial read/write access is achieved by SAM architecture. Read or write cycle is determined when the last read or write transfer operation is executed. If the last transfer operation was read transfer, the serial read cycle is performed until the next write or pseudo write transfer cycle is executed. On the other hand, if the last transfer operation was write or pseudo write or pseudo write transfer, the serial write cycle is performed. In the serial write operation, 256 words by 4 bits data stored in the SAM can be transfered to DRAM under SE="L" condition, and SE="H" condition disables data transfer from SAM to DRAM. The serial access operation can be done asynchronously from DRAM port.

This pin is used as a shift clock for SAM port. The serial access is triggered by the rising edge of SAS. In the write cycle, the data of the SD pins are strobed by the rising edge of SAS and written into the selected cell. In the read cycle, output data become valid after t<sub>SAC</sub> from the rising edge of SAS and the data remain valid until the next cycle is defined. The SAS clock increments the SAM address automatically. When the SAM address exceeds #255 (Most Significant Address) it returnes to #0 (Least Significant Address)

#### SE:

This pin is used to enable serial access operation by bit to bit.  $\overline{SE} = "H"$  disables serial access operation. In the serial read operation, this pin is used for output enable, i.e.,  $\overline{SE} = "H"$  leads SD pins to "High-Z" state.  $\overline{SE} = "L"$  leads SD pins to valid data with specified access time. In the serial write operation, this pin works as write enable control pin.

#### SD0 to SD3;

These are used as data input/output pins for SAM port. Input or output mode is determined by last occured transfer operation, if last transfer operation was read transfer mode, they are output mode. If the write transfer mode was set, SD pins are enabled to write data into SAM.

#### Refresh;

Since the SAM is constructed by dynamic circuitry, the refresh is necessary to maintain the data in it. The refresh of SAM must be done by 256 cycles of SAS clock/4ms in either output or input mode.  $\overline{\rm SE}$  = "H" allows refresh of SAM with SD pins at "High-Z" state.

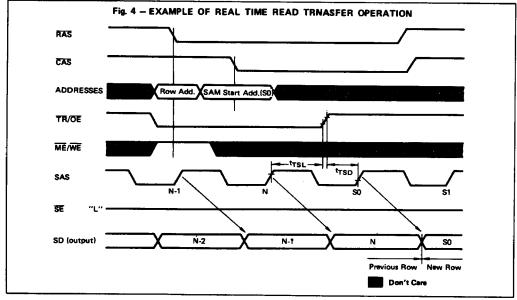

#### Real Time Read Transfer;

This feature is applicable to obtain valid

data continuously when row address is changed without any timing loss from the last bit of previous row to the first bit of new row. Data transfer from DRAM to SAM is triggered by rising edge of TR/OE after the preparation of internal circuit for this operation, while SAM port can continue read operation asynchronously from the above mentioned internal move, Once TR/OE returns to "H" with the restricted timing specification trsL and trsp refered to SAS clock, SD pins can get the valid output data continuously as shown in Fig. 4. The key issue to achieve this feature is to apply SAS clock continuously with the timing consideration to the rising edge of TR/OE.

FUNCTIONAL TRUTH TABLE FOR SERIAL ACCESS (Asynchronous from DRAM port)

| Falling ed | ge of RAS | SAS    | SE | SD0 to SD3    | Function                  |

|------------|-----------|--------|----|---------------|---------------------------|

| TR/OE      | ME/WE     | 7 5/10 | _  |               |                           |

|            |           | Clock  | L  | Input/Output* | Sequential access enable  |

| н          | ×         | Clock  | Н  | Input/Output* | Sequential access disable |

<sup>\*:</sup> The read or write operation of SAM port is pre-determined by the last occurred transfer cycle. Input mode is for write operation. Output mode is for read operation.

X; Don't Care

# RECOMMENDED OPERATING CONDITIONS (Referenced to $V_{SS}$ )

| Parameter          | Symbol          | Min. | Тур. | Max. | Unit | Operating Temperature |

|--------------------|-----------------|------|------|------|------|-----------------------|

|                    | Vcc             | 4.5  | 5.0  | 5.5  | ٧    |                       |

| Supply Voltage     | V <sub>SS</sub> | 0    | 0    | 0    | V    | 0°C to +70°C          |

| Input High Voltage | V <sub>IH</sub> | 2.4  |      | 6.5  | ٧    | ] 0010+700            |

| Input Low Voltage  | ViL             | -2.0 |      | 0.8  | ٧    | }                     |

# CAPACITANCE (TA=25°C)

|                                                |                  |     | м   | Unit |      |  |

|------------------------------------------------|------------------|-----|-----|------|------|--|

| Paramter                                       | Symbol           | Тур | DIP | ZIP  | Unit |  |

| Input Capacitance (A0 to A7)                   | C <sub>IN1</sub> | 1   | 7   | 8    | pF   |  |

| Input Capacitance (RAS, CAS, ME/WE, SE, TR/OE) | C <sub>IN2</sub> |     | 10  | 12   | pF   |  |

| Input Capacitance (SAS)                        | C <sub>IN3</sub> |     | 7   | 7    | pF   |  |

| Input/Output Capacitance (MD0/DQ0 to MD3/DQ3)  | C <sub>IO1</sub> |     | 7   | 8    | pF   |  |

| Input/Output Capacitance (SD0 to SD3)          | C <sub>102</sub> |     | 7   | 8    | pF   |  |

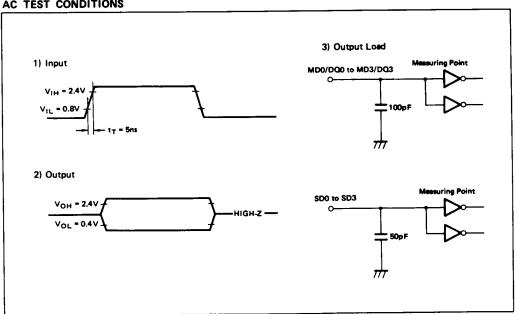

### AC TEST CONDITIONS

# DC CHARACTERISTICS (Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                               |             | Symbol            | Min       | Max      | Unit |

|---------------------------------------------------------------------------------------------------------|-------------|-------------------|-----------|----------|------|

| SAM STANDBY SE = VIH, SAS = VIL                                                                         |             |                   | •         |          |      |

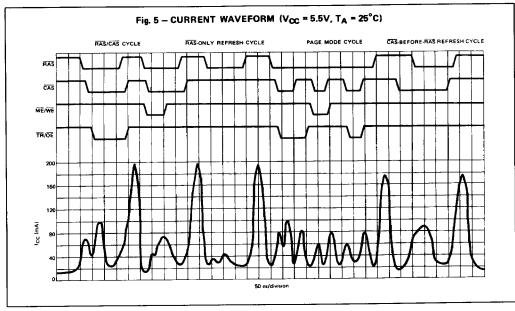

| OPERATING CURRENT* Average power supply current                                                         | MB 81461-12 | I <sub>cc1</sub>  |           | 95       | mA   |

| (RAS, CAS cycling; t <sub>RC</sub> = min)                                                               | MB 81461-15 |                   |           | 85       |      |

| STANDBY CURRENT Power supply current (RAS = CAS = V <sub>IH</sub>                                       | )           | I <sub>CC2</sub>  |           | 20       | mA   |

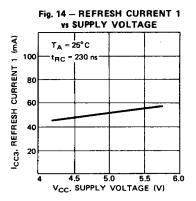

| REFRESH CURRENT 1*                                                                                      | MB 81461-12 |                   |           | 77       |      |

| Average power supply current $(\overline{CAS} = V_{IH}, \overline{RAS} \text{ cycling}; t_{RC} = \min)$ | MB 81461-15 | l <sub>CC3</sub>  |           | 70       | mA   |

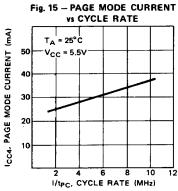

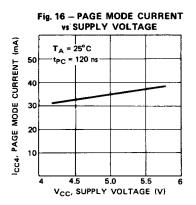

| PAGE MODE CURRENT* Average power supply current                                                         | MB 81461-12 |                   |           | 50       |      |

| $\overline{(RAS} = V_{IL}, \overline{CAS} = \text{cycling}, t_{PC} = \text{min})$                       | MB 81461-15 | l <sub>CC4</sub>  |           | 45       | mA   |

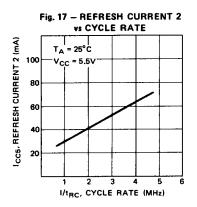

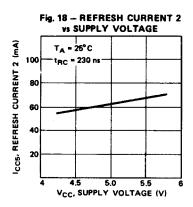

| REFRESH CURRENT 2* Average power supply current                                                         | MB 81461-12 |                   |           | 77       |      |

| (CAS-before-RAS; t <sub>RC</sub> = min)                                                                 | MB 81461-15 | 1 <sub>CC5</sub>  |           | 70       | mA   |

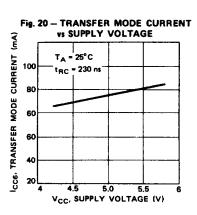

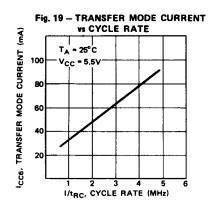

| TRANSFER MODE CURRENT                                                                                   | MB 81461-12 |                   |           | 110      |      |

| Average power supply current<br>(RAS, CAS cycling; t <sub>RC</sub> = min)                               | MB 81461-15 | Icce              |           | 100      | mA   |

| SAM ACTIVE SE = VIL, tSC = min                                                                          | •           |                   |           | <u> </u> |      |

| OPERATING CURRENT* Average power supply current                                                         | MB 81461-12 |                   |           | 130      |      |

| (RAS, CAS cycling; t <sub>RC</sub> = min)                                                               | MB 81461-15 | l <sub>CC7</sub>  |           | 110      | → mA |

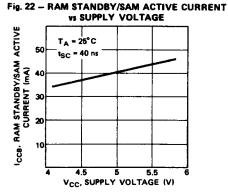

| STANDBY CURRENT Power supply current                                                                    | MB 81461-12 |                   |           | 50       |      |

| (RAS = CAS = V <sub>IH</sub> )                                                                          | MB 81461-15 | l <sub>cc8</sub>  |           | 40       | mA   |

| REFRESH CURRENT 1* Average power supply current                                                         | MB 81461-12 |                   |           | 112      |      |

| (CAS = V <sub>IH</sub> , RAS cycling; t <sub>RC</sub> = min)                                            | MB 81461-15 | cce               |           | 95       | mA   |

| PAGE MODE CURRENT* Average power supply current                                                         | MB 81461-12 |                   |           | 85       |      |

| (RAS = V <sub>IL</sub> , CAS cycling, t <sub>PC</sub> = min)                                            | MB 81461-15 | I <sub>CC10</sub> |           | 70       | mA   |

| REFRESH CURRENT 2*                                                                                      | MB 81461-12 |                   | · · · · · | 112      |      |

| Average power supply current (CAS-before-RAS; t <sub>RC</sub> = min)                                    | MB 81461-15 | l <sub>cc11</sub> |           | 95       | mA   |

| TRANSFER MODE CURRENT                                                                                   |             |                   |           | 145      |      |

| Average power supply current (RAS, CAS cycling; t <sub>RC</sub> = min)                                  | MB 81461-15 | fcc12             | CC12 12   |          | mA   |

# DC CHARACTERISTICS (Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                                                                                    | Symbol                             | Min | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|------|

| INPUT LEAKAGE CURRENT Input leakage current, any input (0V $\leq$ V <sub>IN</sub> $\leq$ 5.5V, V <sub>CC</sub> =5.5V, V <sub>SS</sub> =0V, all other pins not under test=0V) | I <sub>I(L)</sub>                  | -10 | 10  | μΑ   |

| OUTPUT LEAKAGE CURRENT (Data out is disabled, $0  \text{V} \leq \text{V}_{\text{OUT}} \leq 5.5 \text{V}$ )                                                                   | l <sub>O(L)</sub>                  | -10 | 10  | μΑ   |

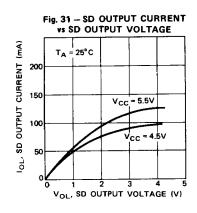

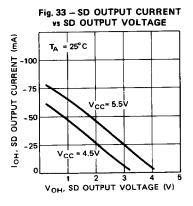

| OUTPUT LEVELS  Output high voltage (I <sub>OH</sub> =-5mA/-2mA for DQi/SDi)  Output low voltage (I <sub>OL</sub> =4.2mA)                                                     | V <sub>OH</sub><br>V <sub>OL</sub> | 2.4 | 0.4 | V    |

Note: I<sub>CC</sub> is dependent on output loading and cycle rates. Specified values are obtained with the output open.

# **AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

|                                        | 1                 | MB 8 | MB 81461-12 |     | 1461-15 | Unit |

|----------------------------------------|-------------------|------|-------------|-----|---------|------|

| Parameter Parameter                    | Symbol            | Min  | Max         | Min | Max     | Unit |

| Time between Refresh (RAM/SAM)         | t <sub>REF</sub>  |      | 4           |     | 4       | ms   |

| Random Read/Write Cycle Time           | t <sub>RC</sub>   | 230  |             | 260 |         | ns   |

| Read-Modify-Write Cycle Time           | tewc              | 305  |             | 345 |         | ns   |

| Page Mode Cycle Time                   | t <sub>PC</sub>   | 120  |             | 145 |         | ns   |

| Page Mode Read-Modify-Write Cycle Time | t <sub>PRWC</sub> | 195  |             | 225 |         | ns   |

| Access Time from RAS                   | t <sub>RAC</sub>  |      | 120         |     | 150     | ns   |

| Access Time from CAS                   | t <sub>CAC</sub>  |      | 60          |     | 75      | ns   |

| Output Buffer Turn Off Delay           | t <sub>OFF</sub>  | 0    | 25          | 0   | 35      | ns   |

| Transition Time                        | t <sub>T</sub>    | 3    | 50          | 3   | 50      | ns   |

| RAS Precharge Time                     | tap               | 90   |             | 100 |         | ns   |

| RAS Pulse Width                        | tras              | 120  | 60000       | 150 | 60000   | ns   |

| RAS Hold Time                          | t <sub>RSH</sub>  | 60   |             | 75  |         | ns   |

| Parameter NOTES                          | Sb-1             | мвя | 31461-12 | MB 8 | 1461-15 |      |

|------------------------------------------|------------------|-----|----------|------|---------|------|

| Parameter NOTES                          | Symbol           | Min | Max      | Min  | Max     | Unit |

| CAS Precharge Time<br>(Normal cycle)     | t <sub>CPN</sub> | 40  |          | 50   |         | ns   |

| CAS Precharge Time<br>(Page mode only)   | t <sub>CP</sub>  | 50  |          | 60   |         | ns   |

| CAS Precharge Time<br>(CAS-before-RAS)   | t <sub>CPR</sub> | 25  |          | 30   |         | ns   |

| CAS Pulse Width                          | t <sub>CAS</sub> | 60  | 60000    | 75   | 60000   | ns   |

| CAS Hold Time                            | t <sub>CSH</sub> | 120 |          | 150  |         | ns   |

| RAS to CAS Delay Time                    | taco             | 22  | 60       | 25   | 75      | ns   |

| CAS to RAS Set Up Time                   | t <sub>CRS</sub> | 10  |          | 10   |         | ns   |

| Row Address Set Up Time                  | t <sub>ASR</sub> | 0   |          | 0    |         | ns   |

| Row Address Hold Time                    | t <sub>RAH</sub> | 12  |          | 15   |         | ns   |

| Column Address Set Up Time               | tASC             | 0   |          | 0    |         | ns   |

| Column Address Hold Time                 | tcah             | 20  |          | 25   |         | ns   |

| Read Command Set Up Time                 | t <sub>RCS</sub> | 0   |          | 0    |         | ns   |

| Read Command Hold Time Referenced to RAS | t <sub>RRH</sub> | 20  |          | 20   |         | ns   |

| Read Command Hold Time Referenced to CAS | t <sub>RCH</sub> | 0   |          | 0    |         | ns   |

| Write Command Set Up Time                | twcs             | -5  |          | -5   |         | ns   |

| Write Command Hold Time                  | twc+             | 30  |          | 35   |         | ns   |

| Write Command Pulse Width                | twe              | 30  |          | 35   |         | ns   |

| Write Command to RAS Lead Time           | t <sub>RWL</sub> | 40  |          | 45   |         | ns   |

| Write Command to CAS Lead Time           | t <sub>CWL</sub> | 40  |          | 45   |         | ns   |

| Data in Set Up Time                      | t <sub>DS</sub>  | 0   |          | 0    |         | ns   |

| Data in Hold Time                        | t <sub>DH</sub>  | 30  |          | 35   |         | ns   |

| Access Time from TR/OE                   | toea             |     | 35       |      | 40      | ns   |

| TR/OE to Data In Delay Time              | t <sub>OED</sub> | 25  |          | 30   |         | ns   |

|                                                        |                  | мв 8 | 1461-12 | мвя | 11461-15 |      |

|--------------------------------------------------------|------------------|------|---------|-----|----------|------|

| Parameter NOTES                                        | Symbol           | Min  | Max     | Min | Max      | Unit |

| Output Buffer Turn Off Delay from TR/OE                | t <sub>OEZ</sub> | 0    | 25      | 0   | 30       | ns   |

| TR/OE Hold Time Referenced to ME/WE                    | t <sub>OEH</sub> | 0    |         | 0   |          | ns   |

| TR/OE to RAS inactive Set Up Time                      | toes             | 0    |         | 0   |          | ns   |

| Data In to CAS Delay Time                              | t <sub>DZC</sub> | 0    |         | 0   |          | ns   |

| Data In to TR/OE Delay Time                            | tozo             | 0    |         | 0   |          | ns   |

| Refresh Set Up Time Referenced to RAS (CAS-before-RAS) | t <sub>FCS</sub> | 25   |         | 30  |          | ns   |

| Refresh Hold Time Referenced to RAS (CAS-before-RAS)   | t <sub>FCH</sub> | 25   |         | 30  |          | ns   |

| RAS Precharge to CAS Active Time                       | <sup>†</sup> RPC | 20   |         | 20  |          | ns   |

| Serial Clock Cycle Time                                | t <sub>sc</sub>  | 40   | 50000   | 60  | 50000    | ns   |

| Access Time from SAS                                   | tsac             |      | 40      |     | 60       | ns   |

| Access Time from SE                                    | tsea             |      | 40      |     | 50       | ns   |

| SAS Precharge Time                                     | t <sub>SP</sub>  | 10   |         | 20  |          | ns   |

| SAS Pulse Width                                        | t <sub>SAS</sub> | 10   |         | 20  |          | ns   |

| SE Precharge Time                                      | tsep             | 25   |         | 45  |          | ns   |

| SE Pulse Width                                         | t <sub>SE</sub>  | 25   |         | 45  |          | ns   |

| Serial Data Out Hold Time<br>after SAS High            | t <sub>SOH</sub> | 10   |         | 10  |          | ns   |

| Serial Output Buffer Turn Off Delay from SE            | t <sub>SEZ</sub> | 0    | 25      | 0   | 30       | ris  |

| Serial Data In Set Up Time                             | t <sub>SDS</sub> | 0    |         | 0   |          | ns   |

| Serial Data In Hold Time                               | t <sub>SDH</sub> | 20   |         | 25  |          | ns   |

| Parameter NOTES                                  | Symbol            | MB 81461-12 |     | MB 81461-15 |     | Unit |

|--------------------------------------------------|-------------------|-------------|-----|-------------|-----|------|

|                                                  |                   | Min         | Max | Min         | Max | Onit |

| Transfer Command (TR) to RAS Set Up Time         | t <sub>TS</sub>   | 0           |     | 0           |     | ns   |

| Transfer Command (TR) to RAS<br>Hold Time        | t <sub>RTH</sub>  | 90          |     | 110         |     | ns   |

| Write Transfer Command (TR) to RAS Hold Time     | † <sub>RTHW</sub> | 12          |     | 15          |     | ns   |

| Transfer Command (TR) to CAS Hold Time           | <sup>t</sup> стн  | 30          |     | 35          |     | ns   |

| Transfer Command (TR) to SAS<br>Lead Time        | t <sub>TSL</sub>  | 5           |     | 10          |     | ns   |

| Transfer Command (TR) to RAS<br>Lead Time        | t <sub>TRL</sub>  | 130         |     | 140         |     | ns   |

| Transfer Command (TR) to RAS Delay Time          | t <sub>TRD</sub>  | -65         |     | -50         |     | ns   |

| First SAS Edge to Transfer Command<br>Delay Time | t <sub>TSD</sub>  | 25          |     | 35          |     | ns   |

| ME/WE to RAS Set Up Time                         | twsn              | 0           |     | 0           |     | ns   |

| ME/WE to RAS Hold Time                           | t <sub>RWH</sub>  | 12          |     | 15          |     | ns   |

| Mask Data (MD) to RAS Set Up Time                | t <sub>MS</sub>   | 0           |     | 0           |     | ns   |

| Mask Data (MD) to RAS Hold Time                  | t <sub>MH</sub>   | 35          |     | 45          |     | ns   |

| Serial Output Buffer Turn Off Delay from RAS     | t <sub>SDZ</sub>  | 10          | 60  | 10          | 75  | ns   |

| Serial Output Buffer Turn On Delay from RAS      | <sup>t</sup> sro  | 0           |     | 0           |     | ns   |

| SAS to RAS Set Up Time                           | t <sub>SRS</sub>  | 40          |     | 60          |     | ns   |

| RAS to SAS Delay Time 12                         | t <sub>SRD</sub>  | 30          |     | 45          |     | ns   |

| Serial Data Input to SE Delay Time               | tsze              | 0           |     | 0           |     | ns   |

| Serial Data Input Delay from RAS 12              | t <sub>SDD</sub>  | 60          |     | 75          |     | ns   |

| Parameter VCTES                                 |        | Symbol            | MB 81461-12 |     | MB 81461-15 |     |      |

|-------------------------------------------------|--------|-------------------|-------------|-----|-------------|-----|------|

|                                                 | VOTES. |                   | Min         | Max | Min         | Max | Unit |

| Serial Data Input to RAS Delay Time             | 13     | t <sub>SZS</sub>  | 0           |     | 0           |     | ns   |

| Pseudo Transfer Command (SE) to RAS Set up Time | 14     | t <sub>ESR</sub>  | 0           |     | 0           |     | ns   |

| Pseudo Transfer Command (SE) to RAS Hold Time   | 14     | <sup>†</sup> REH  | 12          |     | 15          |     | ns   |

| Serial Write Enable Set up Time                 | 11     | t <sub>sws</sub>  | 20          |     | 30          |     | ns   |

| Serial Write Enable Hold Time                   | 111    | tswH              | 80          |     | 120         |     | ns   |

| Serial Write Disable Set Up Time                | 111    | t <sub>swis</sub> | 20          |     | 30          |     | ns   |

| Serial Write Disable Hold Time                  | 11     | tswin             | 40          |     | 60          |     | ns   |

| Asynchronous Command (TR) to RAS Set Up Time    |        | t <sub>YS</sub>   | 0           |     | 0           |     | ns   |

| Asynchronous Command (TR) to RAS Hold Time      |        | t <sub>УН</sub>   | 12          |     | 15          |     | ns   |

| Time between Transfer                           | 15     | t <sub>REFT</sub> |             | 4   |             | 4   | ms   |

#### NOTES:

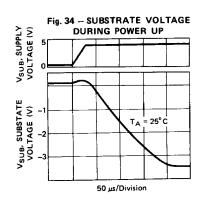

- An initial pause of 200µs is required after power-up followed by any 8 RAS, 8 transfer, and 8 SAS cycle before proper device operation is achieved. In case of using internal refresh counter, a minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycle are required

- 2 AC characteristics assume

- V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> (min) and V<sub>IL</sub> (max).

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> will be increased by the amount that t<sub>RCD</sub> exceeds the value shown.

- S Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- Measured with a load equivalent to 2 TTL loads and 100pF.

- Operation within the t<sub>RCD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- $t_{RCD}$  (min) =  $t_{RAH}$  (min) +  $2t_{T}$  ( $t_{T}$ =5ns) +  $t_{ASC}$  (min) Either  $t_{RRH}$  or  $t_{RCH}$  must be satisfied for a read cycle.

- Measured with a load equivalent to 2 TTL loads and 50pF.

- 11 Input mode only

- 12 Write transfer and pseuso write transfer only.

- Read transfer only in the case that the previous transfer was write transfer.

- Pseudo write transfer only.

- III If treft is not satisfied, 8 transfer and 8 SAS cycles before proper device operation is needed.

- Either t<sub>DZC</sub> or t<sub>DZO</sub> must be satisfied.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

Note 2) When TR/OE is kept "H" through a cycle, the MD/DQ are kept High-Z state.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

Note 2) When TR/OE is kept "H" through a cycle, the MD/DQ are kept High-Z state.

Note 1) When ME/WE = "H", all data on the MD/DQ can be written into the cell.

When ME/WE = "L", the data on the MD/DQ are not written (masked) except for when MD/DQ = "H" at the falling edge of RAS.

- \*: In the case that the previous transfer is read transfer.

- \*\*: If SE is low, the valid data will appear within tSAC or tSEA.

- \*; In the case that the previous transfer is write transfer.

- \*\*; If SE is low and the previous cycle is serial write cycle, this should be valid data input.

- \*; In the case that the previous transfer is write transfer.

- \*\*; If SE is high these data are not written into the SAM.

- \*: If SE is high, these data are not written into SAM.

- \*\*: If SE is high, SD (SD0 to SD3) are in High-Z state after t<sub>SEZ</sub>.

- If  $\overline{\text{SE}}$  becomes low, the valid data will appear meeting  $t_{\text{SAC}}$  and  $t_{\text{SEA}}$ .

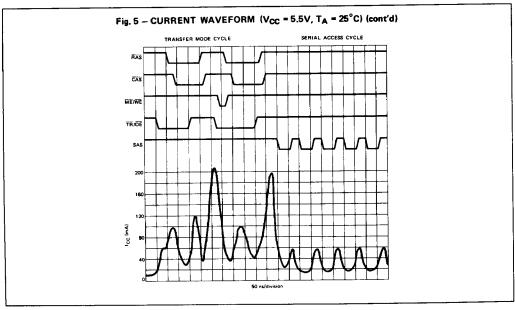

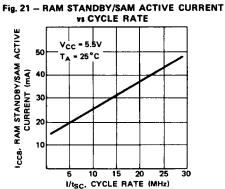

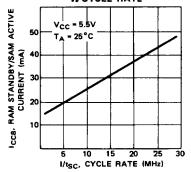

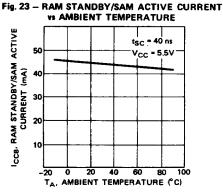

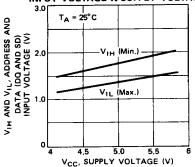

# TYPICAL CHARACTERISTICS CURVES

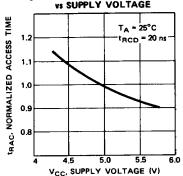

Fig. 6 - NORMALIZED ACCESS TIME VS SUPPLY VOLTAGE

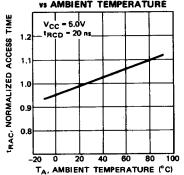

Fig. 7 - NORMALIZED ACCESS TIME VS AMBIENT TEMPERATURE

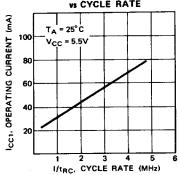

Fig. 8 - OPERATING CURRENT VS CYCLE RATE

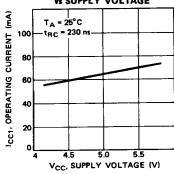

Fig. 9 - OPERATING CURRENT vs SUPPLY VOLTAGE

Fig. 10 - OPERATING CURRENT VS AMBIENT TEMPERATURE

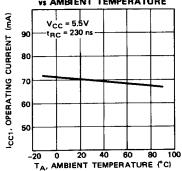

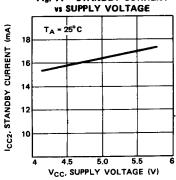

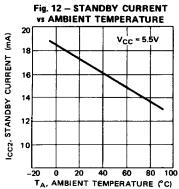

Fig. 11 - STANDBY SURRENT VS SUPPLY VOLTAGE

ICC3, REFRESH CURRENT 1 (mA) TA = 25°C 100 80 60 40 I/tRC, CYCLE RATE (MHz)

Fig. 13 - REFRESH CURRENT 1

VS CYCLE RATE

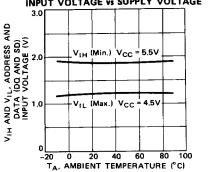

Fig. 24 - ADDRESS AND DATA (DQ AND SD) INPUT VOLTAGE VS SUPPLY VOLTAGE

Fig. 25 -- ADDRESS AND DATA (DQ AND SD)

INPUT VOLTAGE vs SUPPLY VOLTAGE

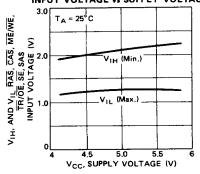

Fig. 26 — RAS, CAS, ME/WE, TR/OE, SE, SAS INPUT VOLTAGE vs SUPPLY VOLTAGE

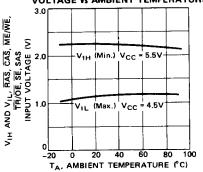

Fig. 27 - RAS, CAS, ME/WE, TR/OE, SE, SAS INPUT **VOLTAGE VS AMBIENT TEMPERATURE**

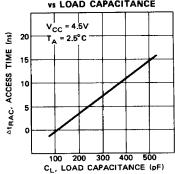

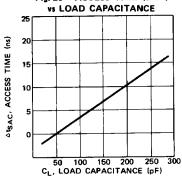

Fig. 28 - ACCESS TIME (RAM) VS LOAD CAPACITANCE

Fig. 29 - ACCESS TIME (SAM) **VS LOAD CAPACITANCE**

## PACKAGE DIMENSIONS

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.