# SH7095 Hardware User Manual

## **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from

accidents or any other reasons during operation of the user's unit according to this

document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## Contents

|      |                 | Overview and Pin Functions                    | 1  |  |  |

|------|-----------------|-----------------------------------------------|----|--|--|

| 1.1  | SH7095 Features |                                               |    |  |  |

|      | 1.1.1           | Features of the SH7095                        | 1  |  |  |

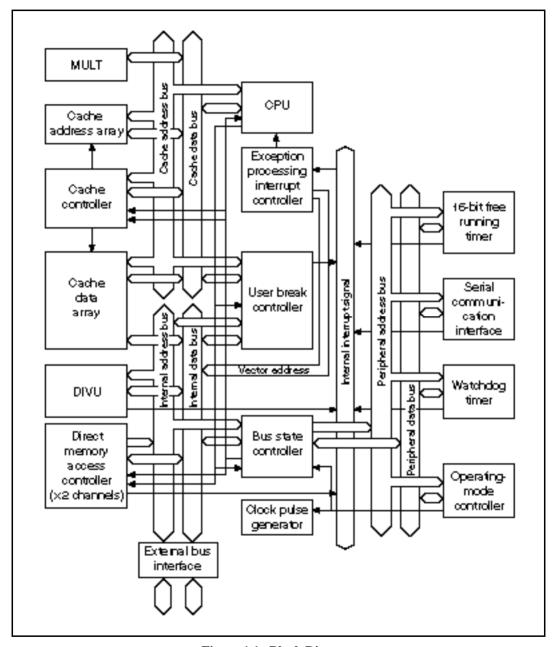

| 1.2  |                 | Diagram                                       | 5  |  |  |

| 1.3  |                 | ption of Pins                                 | 6  |  |  |

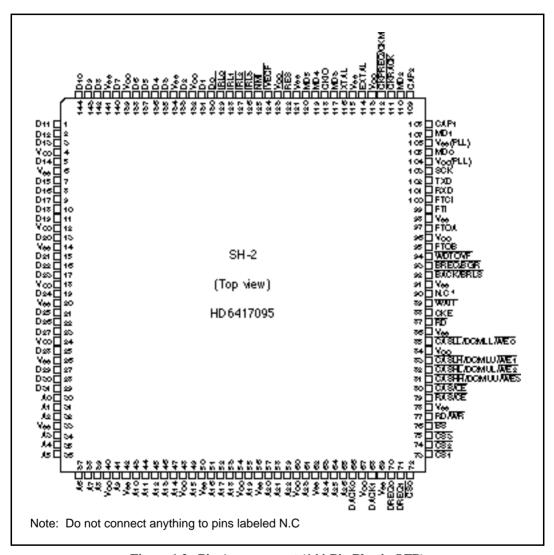

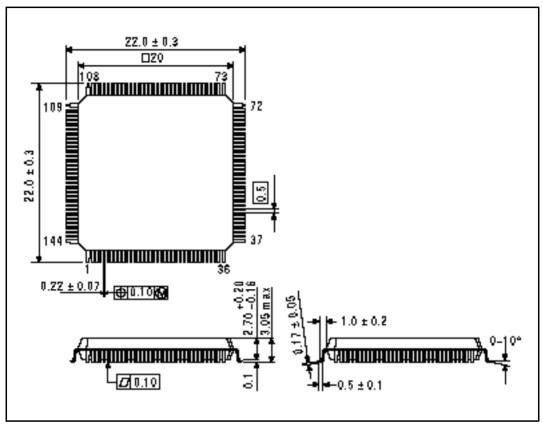

|      | 1.3.1           | Pin Arrangement                               | 6  |  |  |

|      | 1.3.2           | Pin Functions.                                | 7  |  |  |

| Sect | ion 2           | CPU                                           | 13 |  |  |

| 2.1  | Registe         | er Configuration                              | 13 |  |  |

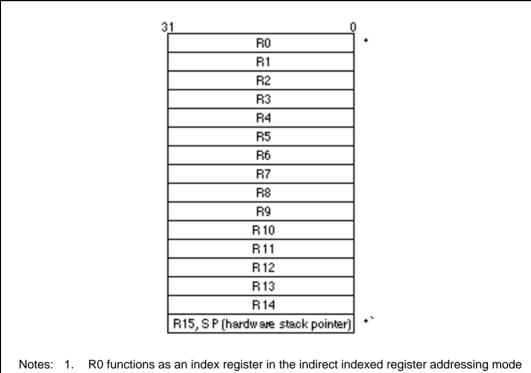

|      | 2.1.1           | General Registers                             | 13 |  |  |

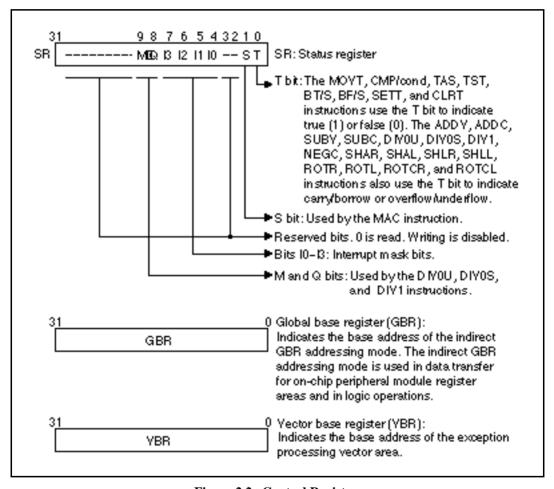

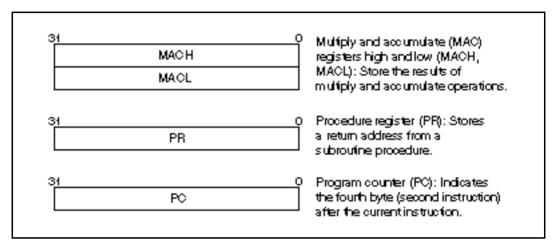

|      | 2.1.2           | Control Registers                             | 14 |  |  |

|      | 2.1.3           | System Registers                              | 14 |  |  |

|      | 2.1.4           | Initial Values of Registers                   | 15 |  |  |

| 2.2  | Data F          | ormats                                        | 16 |  |  |

|      | 2.2.1           | Data Format in Registers                      | 16 |  |  |

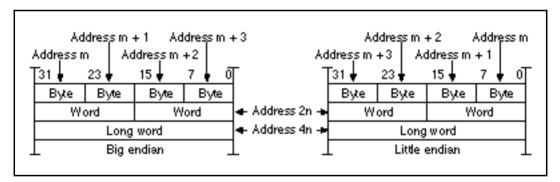

|      | 2.2.2           | Data Format in Memory                         | 16 |  |  |

|      | 2.2.3           | Immediate Data Format                         | 17 |  |  |

| 2.3  | Instruc         | tion Features                                 | 17 |  |  |

|      | 2.3.1           | RISC-Type Instruction Set                     | 17 |  |  |

|      | 2.3.2           | Addressing Modes                              | 20 |  |  |

|      | 2.3.3           | Instruction Format                            | 23 |  |  |

| 2.4  | Instruc         | tion Set                                      | 27 |  |  |

|      | 2.4.1           | Instruction Set by Classification             | 27 |  |  |

|      | 2.4.2           | Operation Code Map                            | 40 |  |  |

| 2.5  | Proces          | sing States                                   | 42 |  |  |

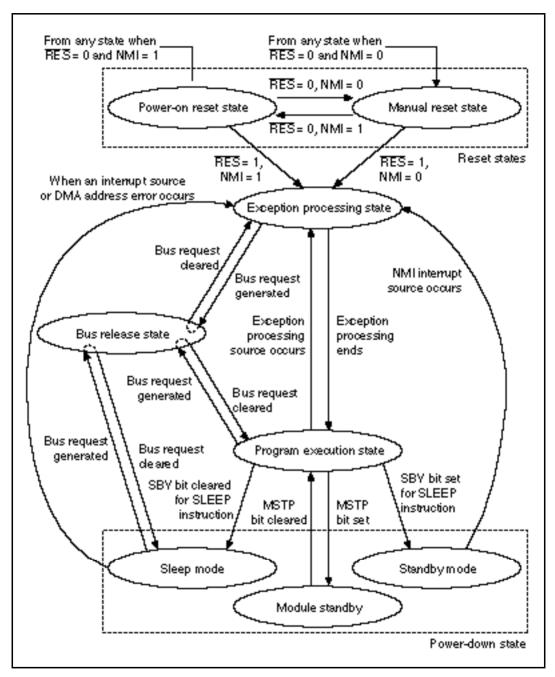

|      | 2.5.1           | State Transitions                             | 42 |  |  |

|      | 2.5.2           | Power-Down State                              | 44 |  |  |

| Sect | ion 3           | Operating Mode                                | 47 |  |  |

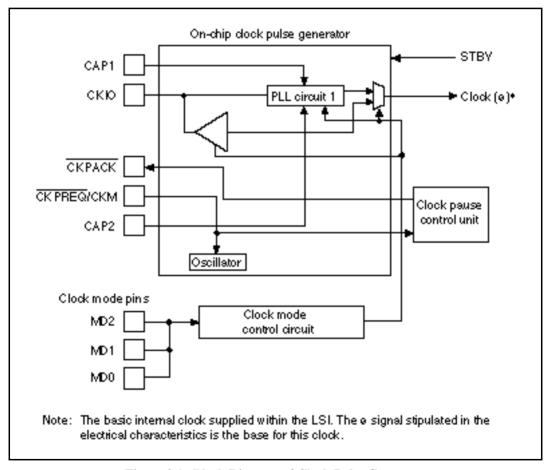

| 3.1  |                 | ing Mode of the On-chip Clock Pulse Generator | 47 |  |  |

|      | 3.1.1           | Clock Pulse Generator                         | 47 |  |  |

|      | 3.1.2           | Clock Operating Mode                          | 49 |  |  |

| 3.2  | Bus W           | idth of the CS0 Area                          | 50 |  |  |

| 3.3  |                 | ing between Master and Slave Modes            | 51 |  |  |

| 3.4  |                 | Control Register.                             | 51 |  |  |

| Sect | ion 4           | Exception Processing                          | 53 |  |  |

|      |                 | ew                                            | 53 |  |  |

|            | 4.1.1           | Types of Exception Processing and Priority Order                                        | 53        |

|------------|-----------------|-----------------------------------------------------------------------------------------|-----------|

|            | 4.1.2           | Exception Processing Operations                                                         | 54        |

|            | 4.1.3           | Exception Processing Vector Table                                                       | 55        |

| 4.2        | Resets          |                                                                                         | 57        |

|            | 4.2.1           | Types of Resets                                                                         | 57        |

|            | 4.2.2           | Power-On Reset                                                                          | 57        |

|            | 4.2.3           | Manual Reset                                                                            | 58        |

| 4.3        | Addre           | ss Errors                                                                               | 59        |

|            | 4.3.1           | Sources of Address Errors                                                               | 59        |

|            | 4.3.2           | Address Error Exception Processing                                                      | 60        |

| 4.4        | Interru         | pts                                                                                     | 60        |

|            | 4.4.1           | Interrupt Sources                                                                       | 60        |

|            | 4.4.2           | Interrupt Priority Level                                                                | 61        |

|            | 4.4.3           | Interrupt Exception Processing                                                          | 61        |

| 4.5        | Except          | tions Triggered by Instructions                                                         | 62        |

|            | 4.5.1           | Instruction-Triggered Exception Types                                                   | 62        |

|            | 4.5.2           | Trap Instructions                                                                       | 62        |

|            | 4.5.3           | Illegal Slot Instructions                                                               | 63        |

|            | 4.5.4           | General Illegal Instructions                                                            | 63        |

| 4.6        | When            | Exception Sources are Not Accepted                                                      | 63        |

|            | 4.6.1           | Immediately after a Delay Branch Instruction                                            | 64        |

|            | 4.6.2           | Immediately after an Interrupt-Disabled Instruction                                     | 64        |

| 4.7        | Stack S         | Status after Exception Processing Ends                                                  | 64        |

| 4.8        | Notes           | on Use                                                                                  | 65        |

|            | 4.8.1           | Value of Stack Pointer (SP)                                                             | 65        |

|            | 4.8.2           | Value of Vector Base Register (VBR)                                                     | 65        |

|            | 4.8.3           | Address Errors Caused by Stacking of Address Error Exception Processing                 | 65        |

|            | 4.8.4           | Accessing Registers during a Manual Reset                                               | 65        |

| Coot       | ion 5           | Interment Controller (INTC)                                                             | <b>67</b> |

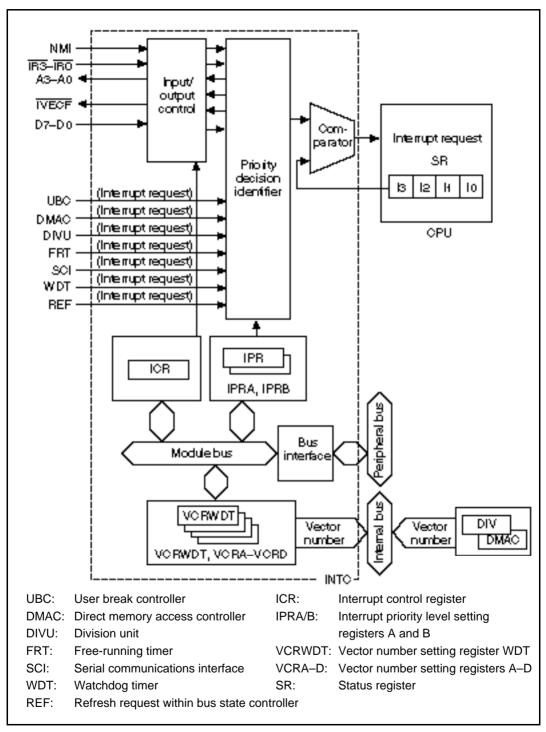

|            |                 | Interrupt Controller (INTC)                                                             | 67        |

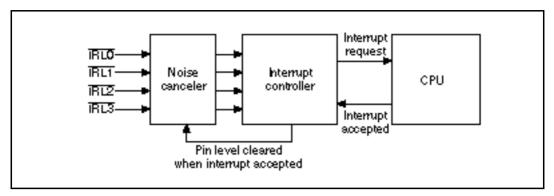

| 5.1        | 5.1.1           | iew                                                                                     | 67        |

|            |                 | Features                                                                                | 67        |

|            | 5.1.2           | Block Diagram.                                                                          | 67        |

|            | 5.1.3           | Pin Configuration                                                                       | 69<br>69  |

| <i>5</i> 2 | 5.1.4           | Register Configuration.                                                                 |           |

| 5.2        |                 | pt Sources                                                                              | 70        |

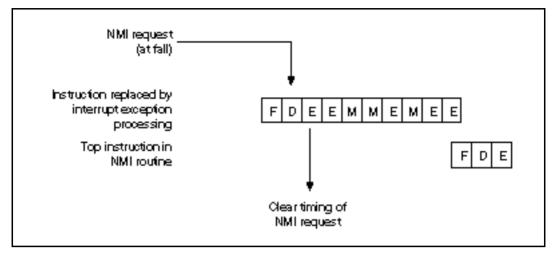

|            | 5.2.1           | NMI Interrupts                                                                          | 70        |

|            | 5.2.2           | User Break Interrupt.                                                                   | 70        |

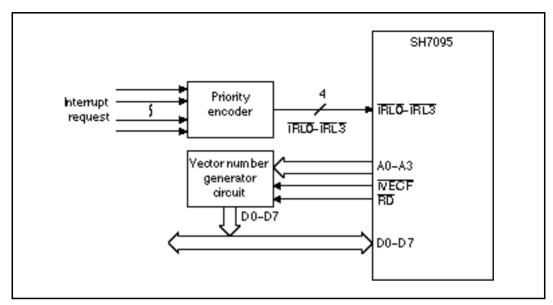

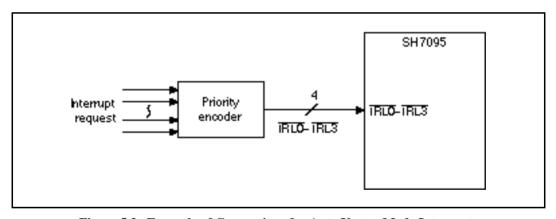

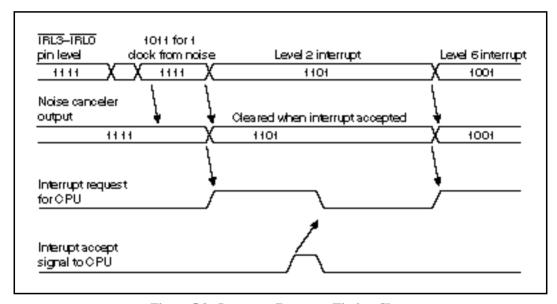

|            | 5.2.3           | IRL Interrupts On this Parisheral Module Interrupts                                     | 71        |

|            | 5.2.4           | On-chip Peripheral Module Interrupts  Interrupt Execution Vectors and Priority Penkings | 74        |

| 5.2        | 5.2.5<br>Deseri | Interrupt Exception Vectors and Priority Rankings                                       | 74<br>76  |

| 5.3        |                 | ption of Registers                                                                      | 76        |

|            | D. S. I         | mierrubi Priority Level Semng Kegisler A (IPKA)                                         | 76        |

|      | 5.3.2   | Interrupt Priority Level Setting Register B (IPRB) | 77  |

|------|---------|----------------------------------------------------|-----|

|      | 5.3.3   | Vector Number Setting Register WDT (VCRWDT)        | 79  |

|      | 5.3.4   | Vector Number Setting Register A (VCRA)            | 79  |

|      | 5.3.5   | Vector Number Setting Register B (VCRB)            | 80  |

|      | 5.3.6   | Vector Number Setting Register C (VCRC)            | 81  |

|      | 5.3.7   | Vector Number Setting Register D (VCRD)            | 82  |

|      | 5.3.8   | Interrupt Control Register (ICR)                   | 83  |

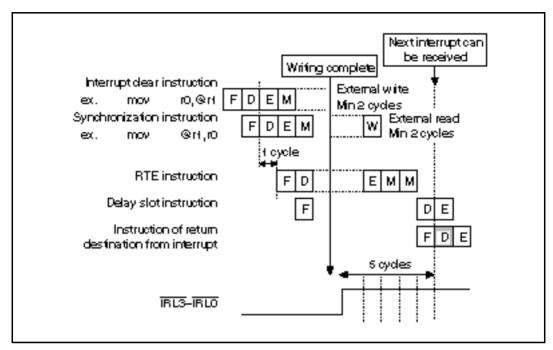

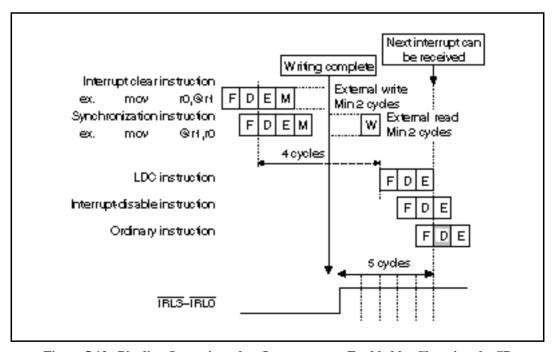

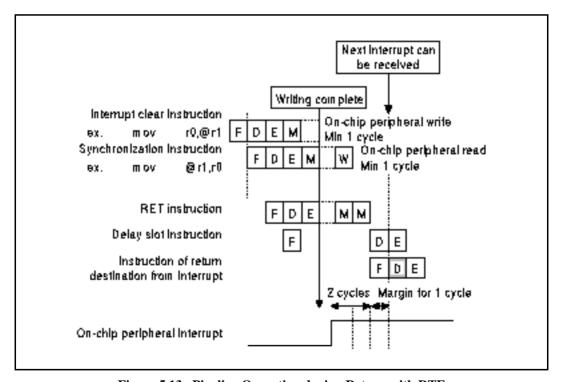

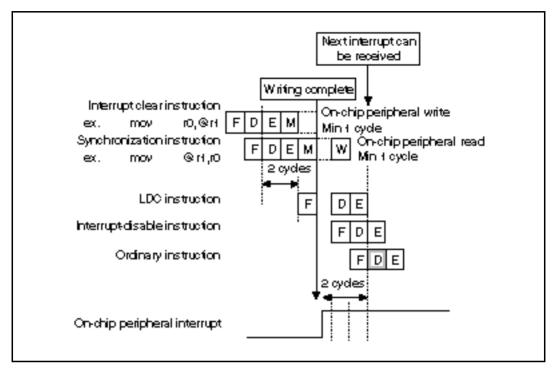

| 5.4  | Interru | upt Operation                                      | 84  |

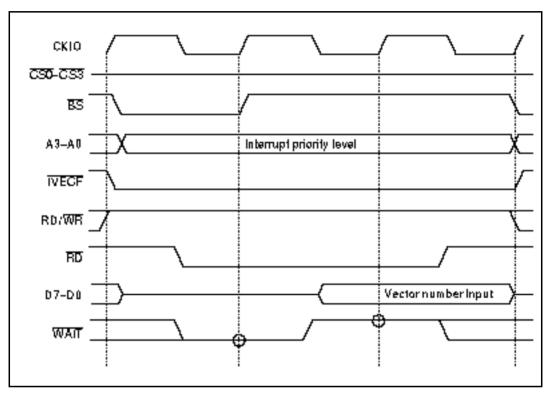

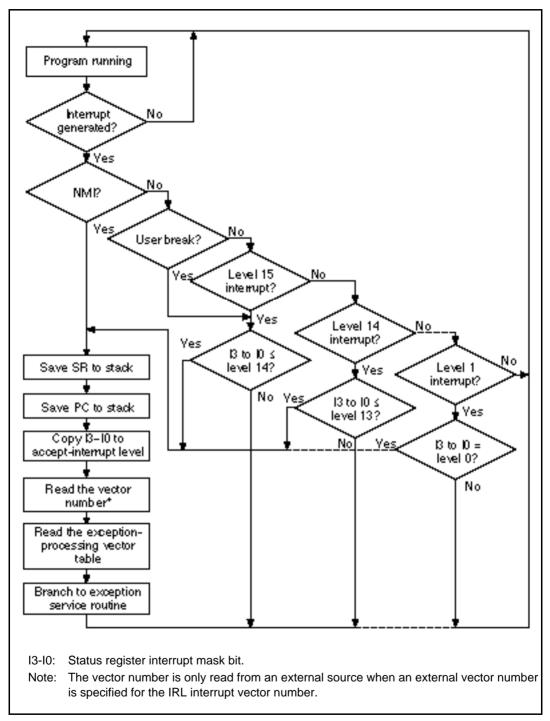

|      | 5.4.1   | Interrupt Sequence                                 | 84  |

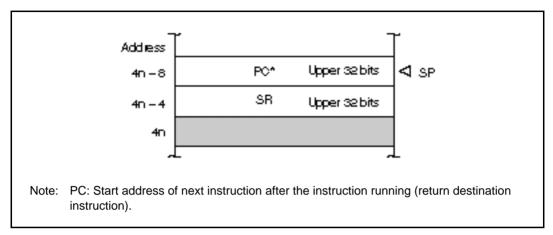

|      | 5.4.2   | Stack after Interrupt Exception Processing         | 87  |

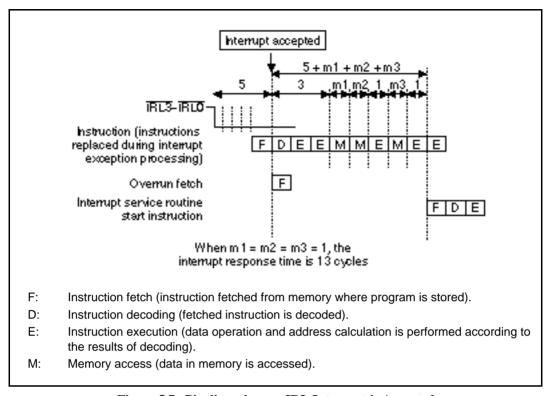

| 5.5  | Interru | upt Response Time                                  | 87  |

| 5.6  |         | ling of the IRL Pins (0–3)                         | 89  |

| 5.7  | Notes   | on Use                                             | 90  |

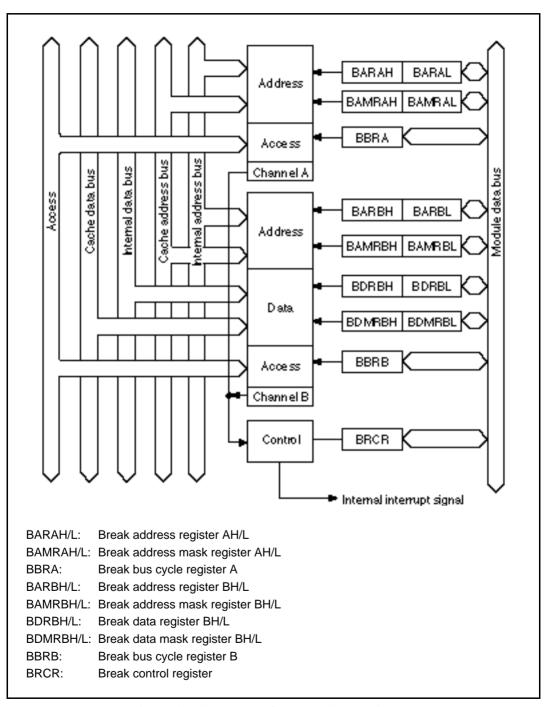

| Sect | ion 6   | User Break Controller                              | 95  |

| 6.1  |         | iew                                                | 95  |

|      | 6.1.1   | Features                                           | 95  |

|      | 6.1.2   | Block Diagram                                      | 96  |

|      | 6.1.3   | Register Configuration                             | 97  |

| 6.2  | Regist  | ter Descriptions                                   | 98  |

|      | 6.2.1   | Break Address Register A (BARA)                    |     |

|      | 6.2.2   | Break Address Mask Register A (BAMRA)              |     |

|      | 6.2.3   | Break Bus Cycle Register A (BBRA)                  |     |

|      | 6.2.4   | Break Address Register B (BARB)                    | 102 |

|      | 6.2.5   | Break Address Mask Register B (BAMRB)              |     |

|      | 6.2.6   | Break Data Register B (BDRB)                       |     |

|      | 6.2.7   | Break Data Mask Register B (BDMRB)                 |     |

|      | 6.2.8   | Bus Break Register B (BBRB)                        |     |

|      | 6.2.9   | Break Control Register (BRCR)                      |     |

| 6.3  | Opera   | tion                                               | 108 |

|      | 6.3.1   | Flow of the User Break Operation.                  |     |

|      | 6.3.2   | Break on Instruction Fetch Cycle                   |     |

|      | 6.3.3   | Break on Data Access Cycle                         |     |

|      | 6.3.4   | Break on External Bus Cycle                        |     |

|      | 6.3.5   | Program Counter (PC) Values Saved                  |     |

|      | 6.3.6   | Use Examples.                                      |     |

|      | 6.3.7   | Notes on Use                                       | 113 |

|      | 6.3.8   | SH7000-Series Compatibility Mode                   |     |

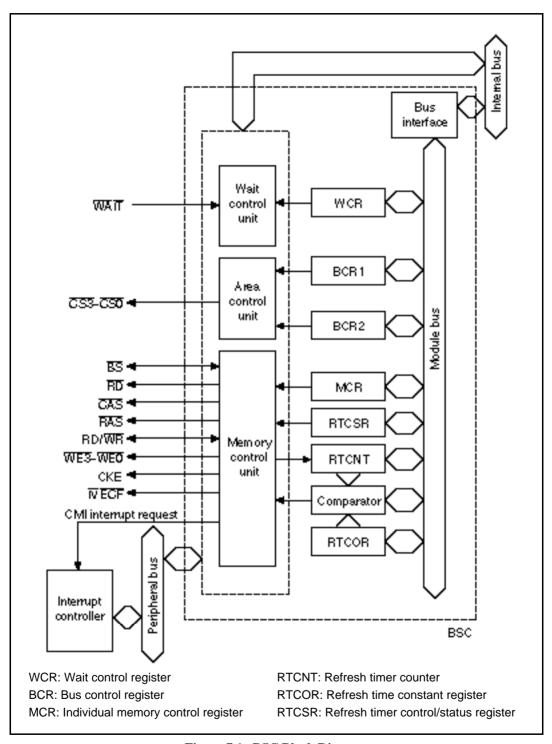

| Sect | ion 7   | Bus State Controller (BSC)                         | 117 |

| 7.1  |         | iew                                                |     |

|      | 7.1.1   | Features                                           | 117 |

|      | 7.1.2   | Block Diagram.                                     |     |

|     | 7.1.3   | Pin Configuration                             | 120 |

|-----|---------|-----------------------------------------------|-----|

|     | 7.1.4   | Register Configuration.                       | 121 |

|     | 7.1.5   | Address Map                                   | 122 |

| 7.2 | Descrip | tion of Registers                             | 124 |

|     | 7.2.1   | Bus Control Register 1 (BCR1)                 | 124 |

|     | 7.2.2   | Bus Control Register 2 (BCR2)                 | 126 |

|     | 7.2.3   | Wait Control Register (WCR)                   | 128 |

|     | 7.2.4   | Individual Memory Control Register (MCR)      | 130 |

|     | 7.2.5   | Refresh Timer Control/Status Register (RTCSR) | 134 |

|     | 7.2.6   | Refresh Timer Counter (RTCNT)                 | 135 |

|     | 7.2.7   | Refresh Time Constant Register (RTCOR)        | 136 |

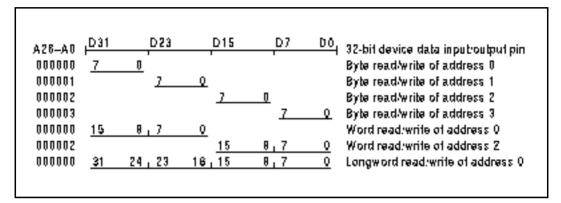

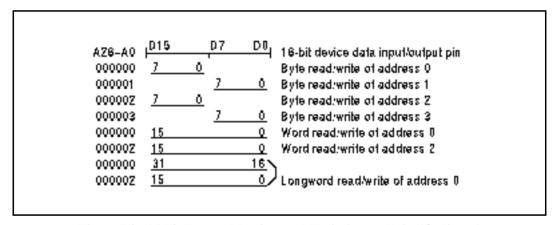

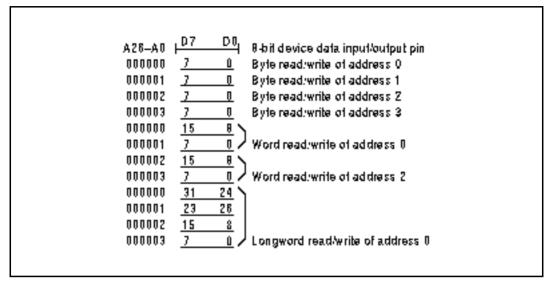

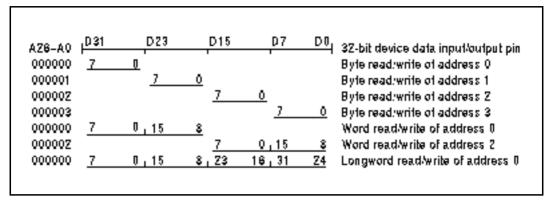

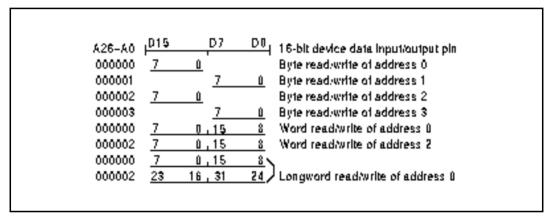

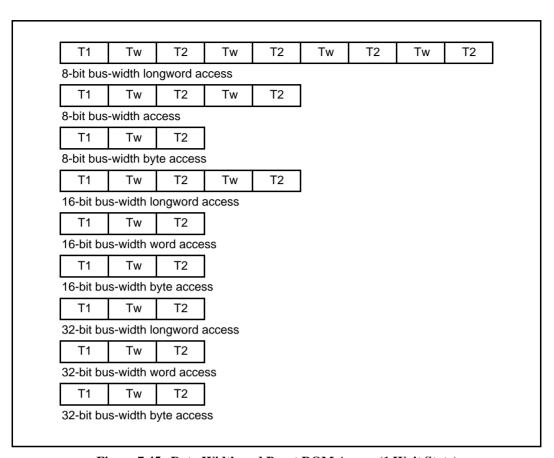

| 7.3 | Access  | Size and Data Alignment                       | 136 |

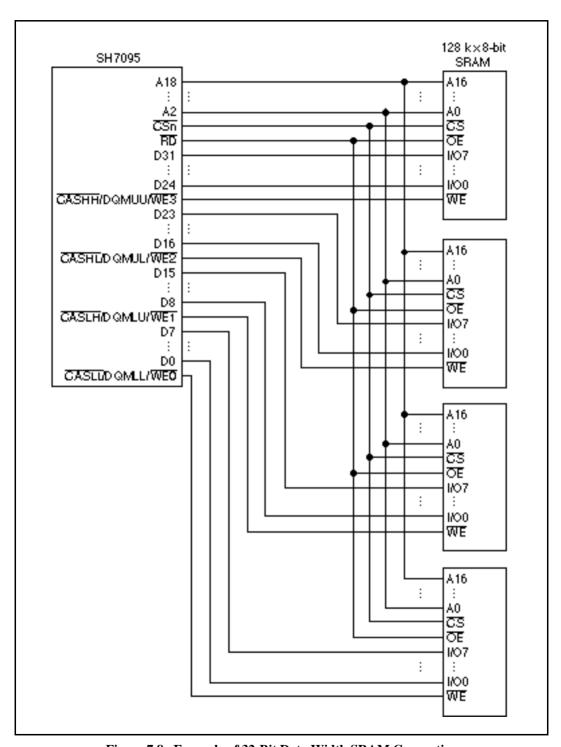

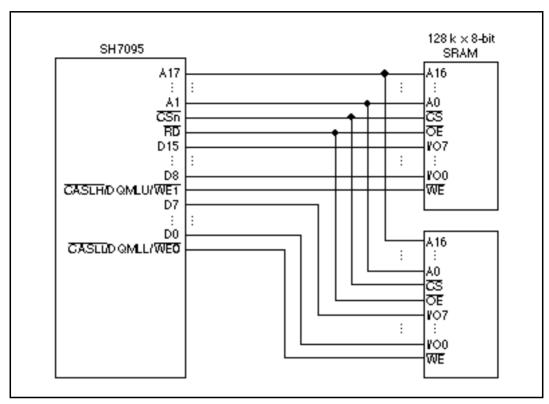

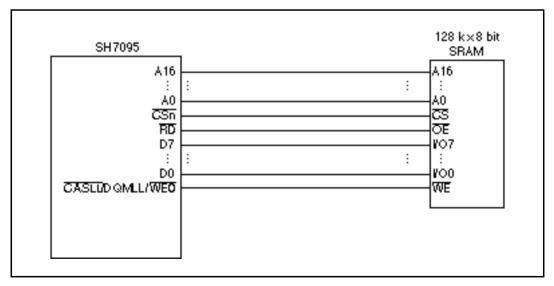

|     | 7.3.1   | Connections to Ordinary Devices.              | 136 |

|     | 7.3.2   | Connections to Little Endian Devices          | 138 |

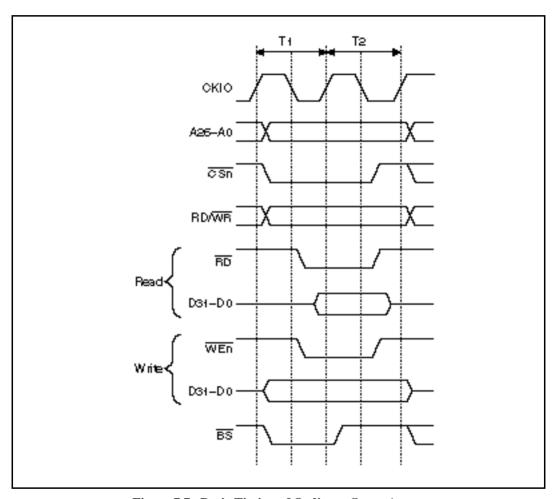

| 7.4 | Accessi | ing Ordinary Space                            | 139 |

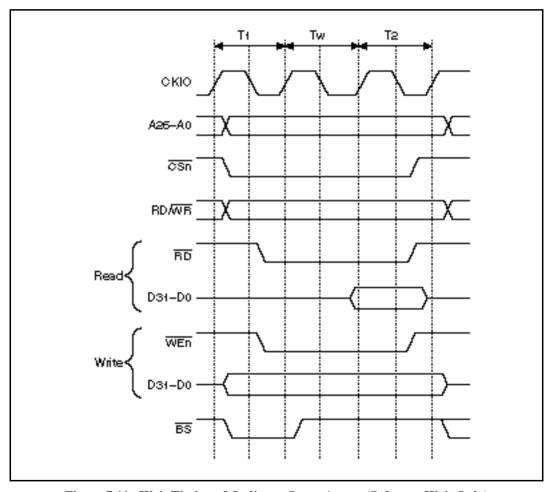

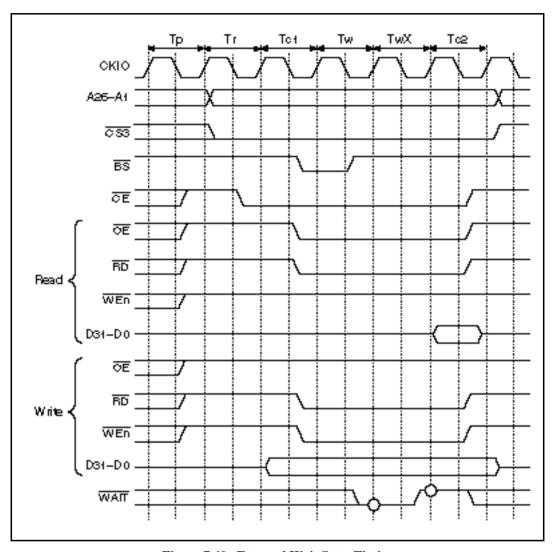

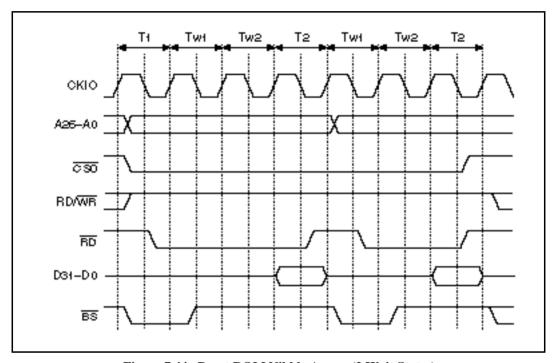

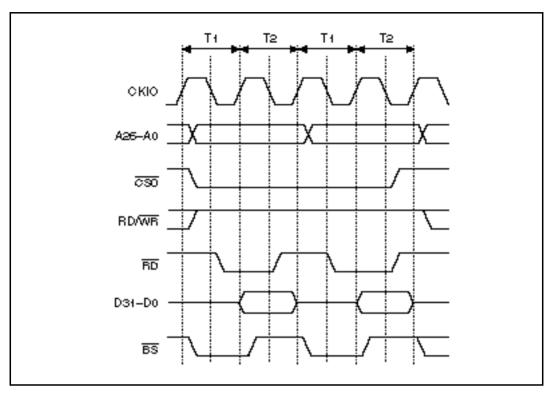

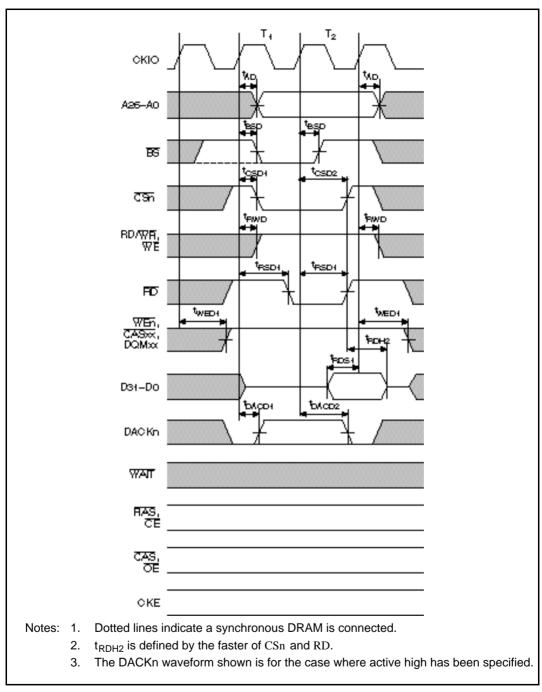

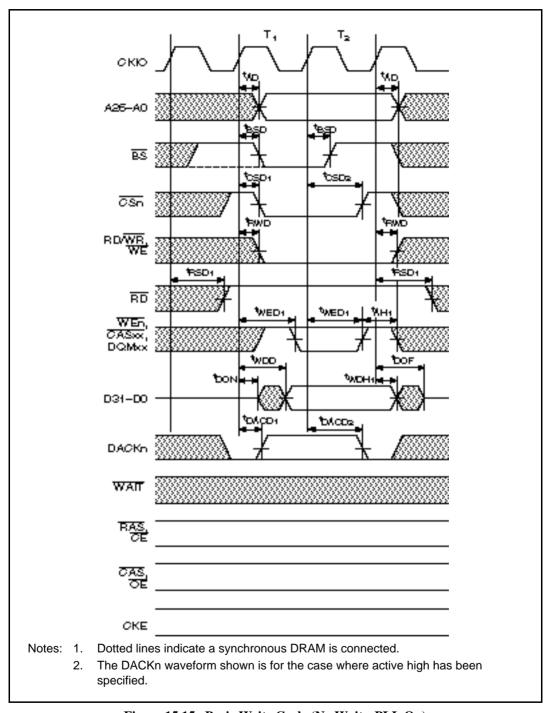

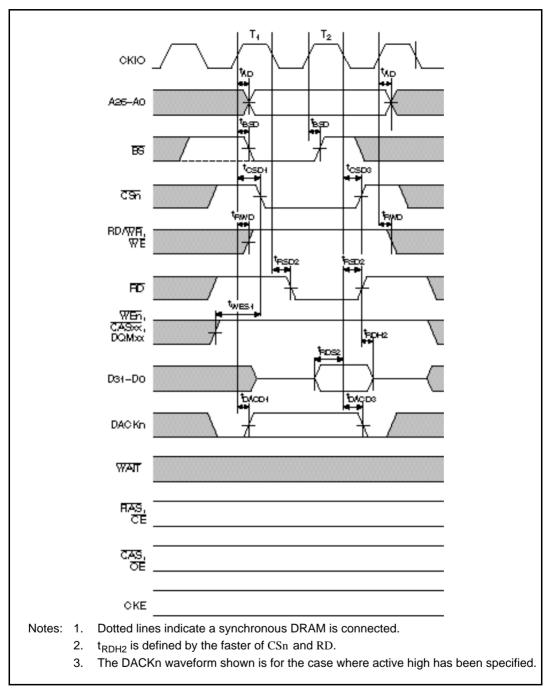

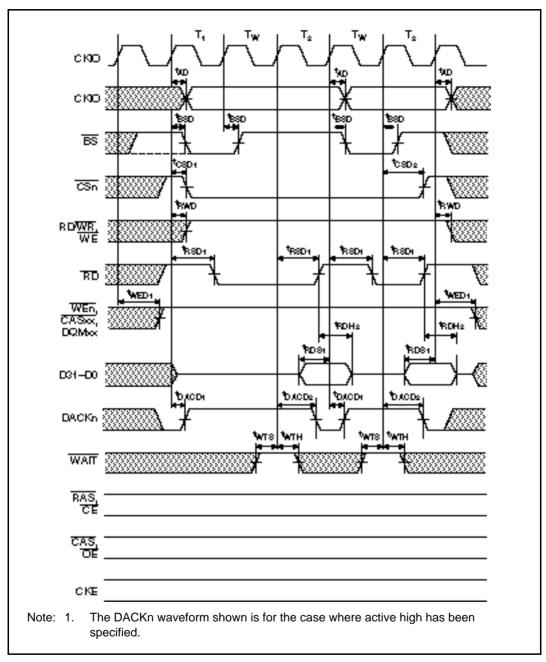

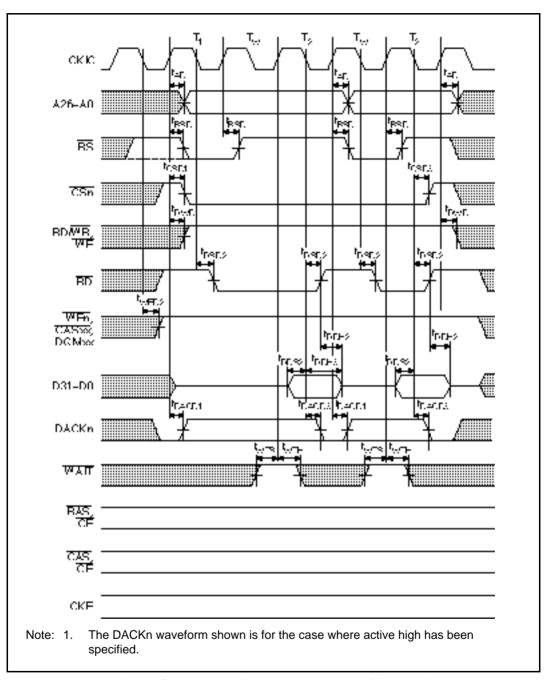

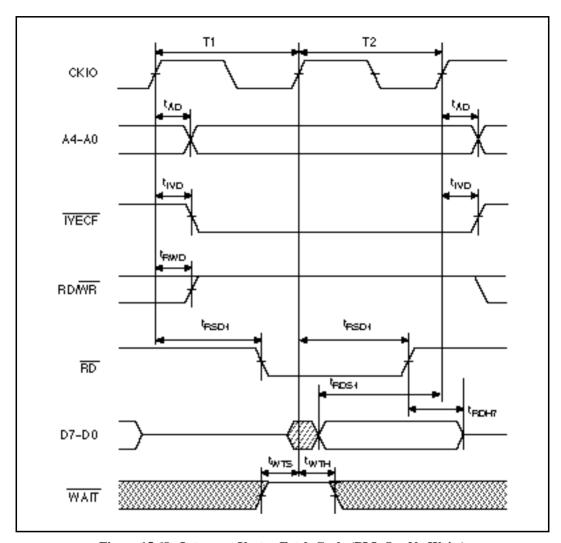

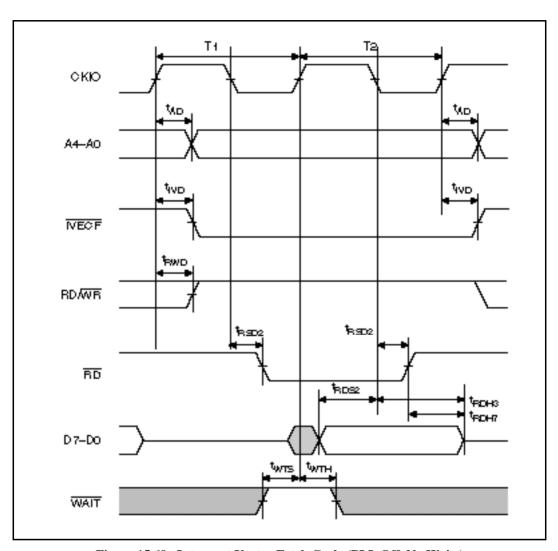

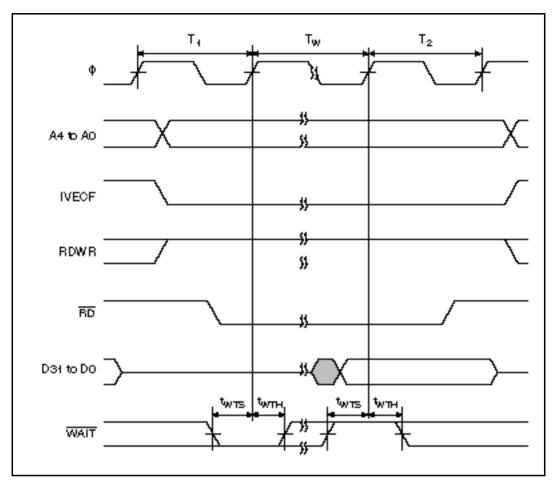

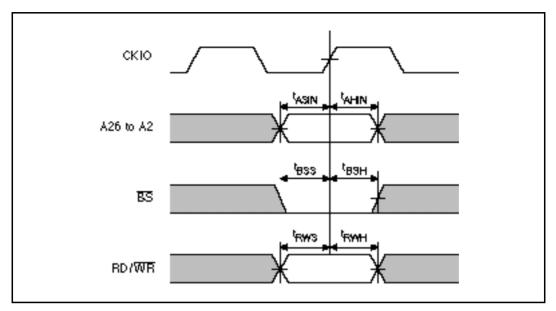

|     | 7.4.1   | Basic Timing                                  | 139 |

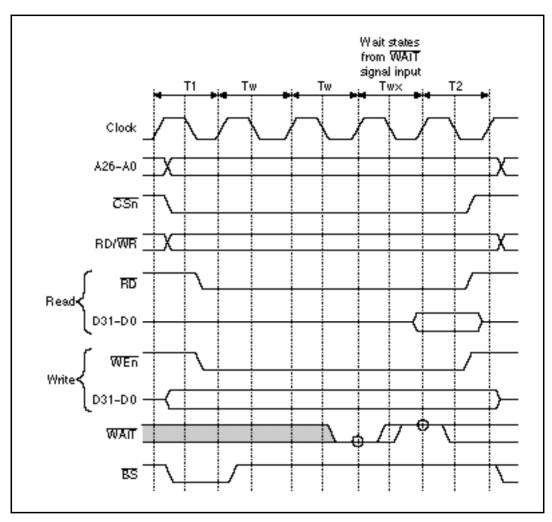

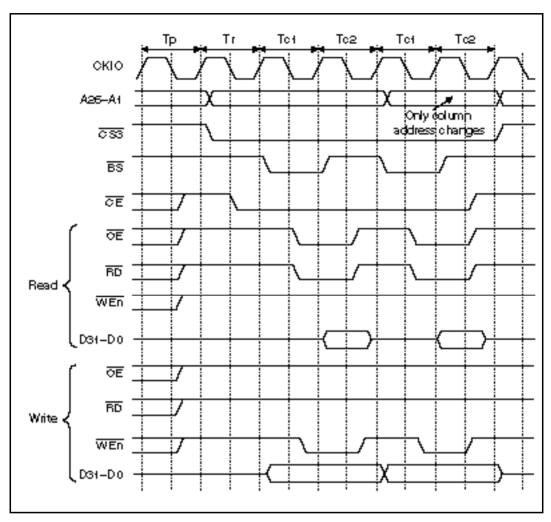

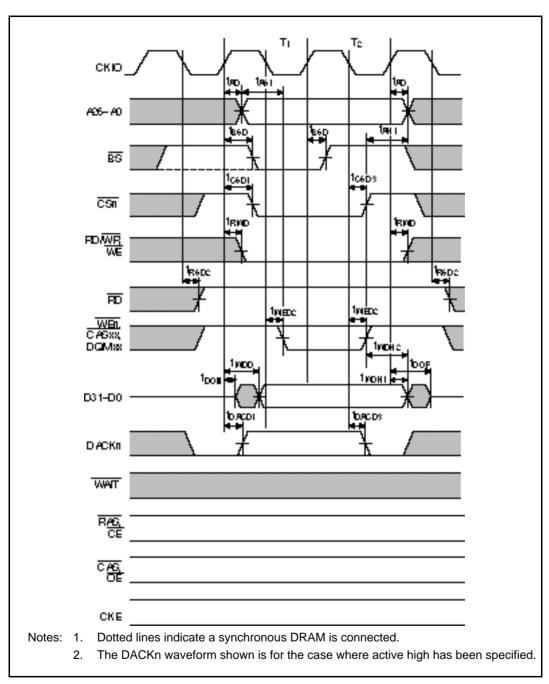

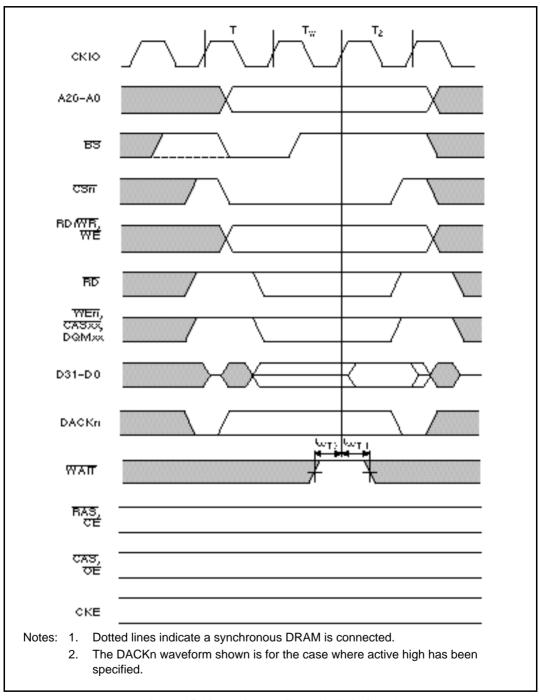

|     | 7.4.2   | Wait State Control                            | 143 |

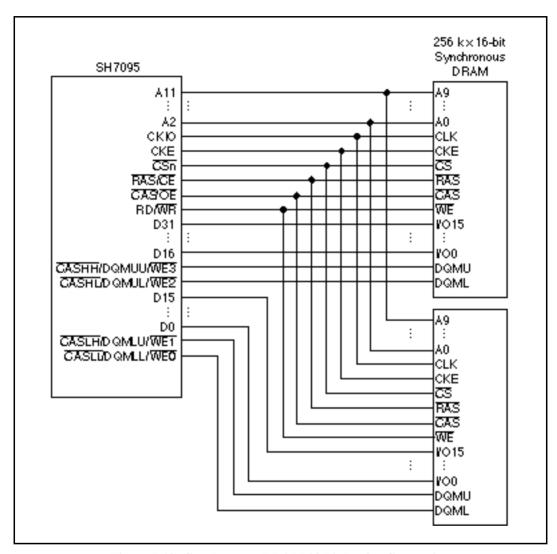

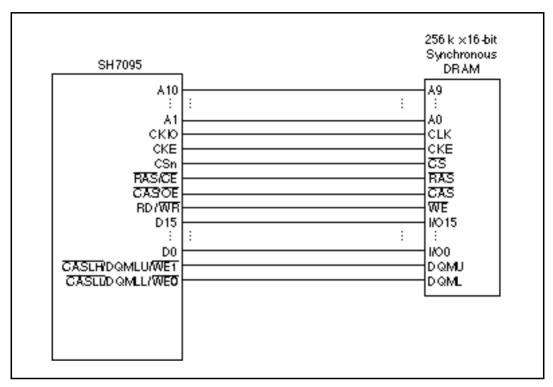

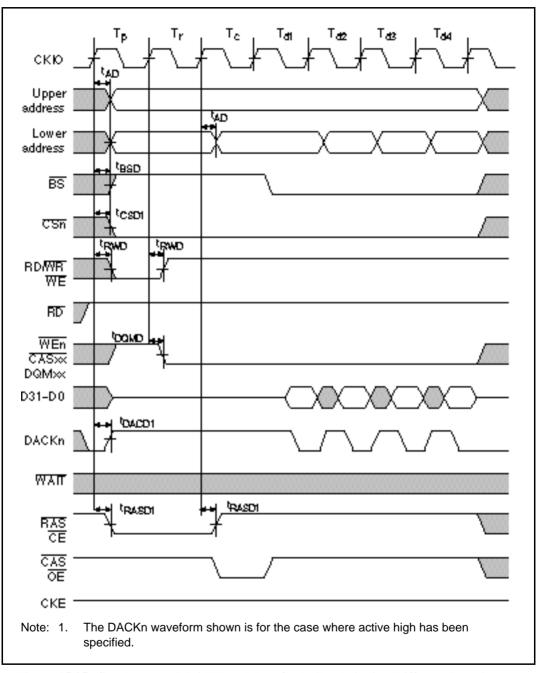

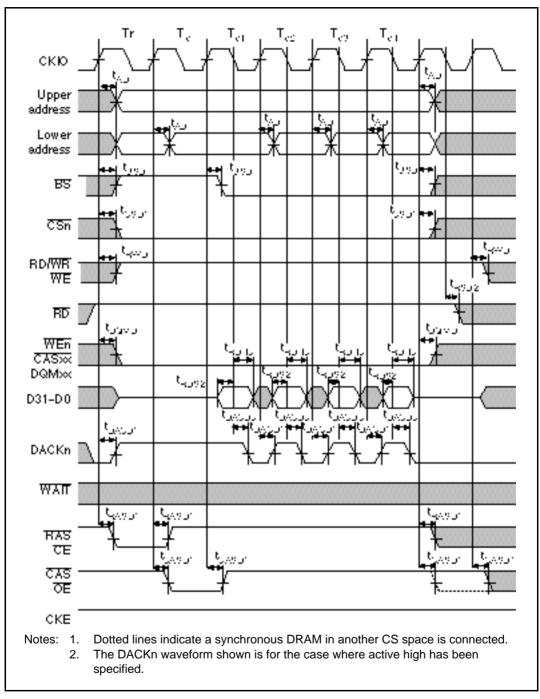

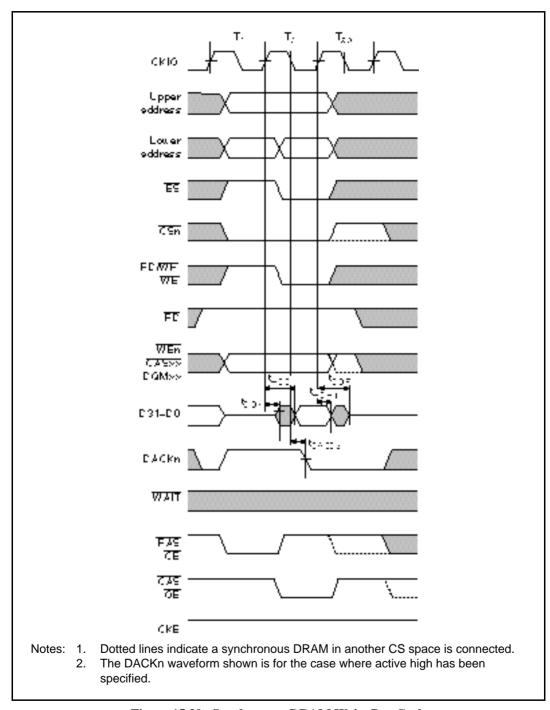

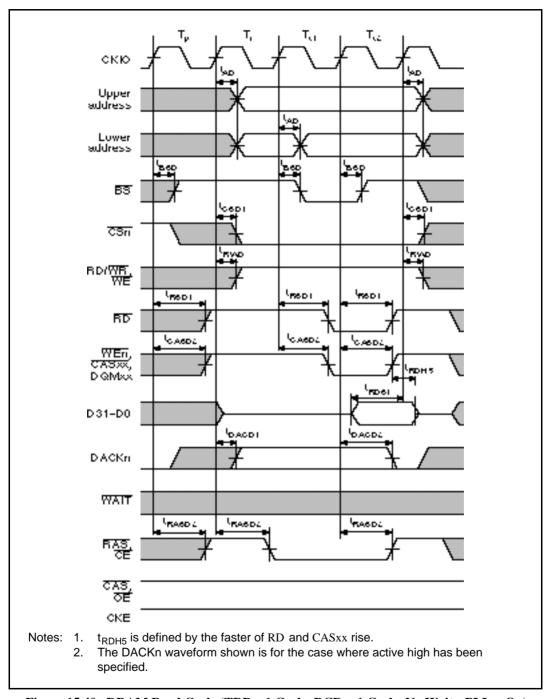

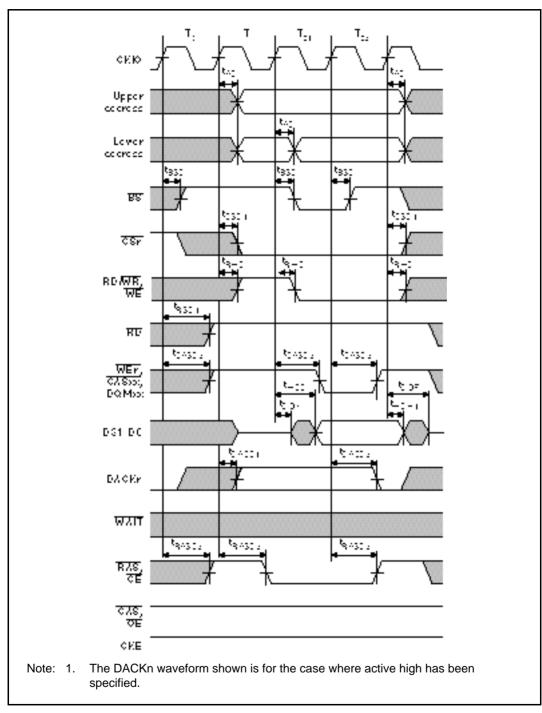

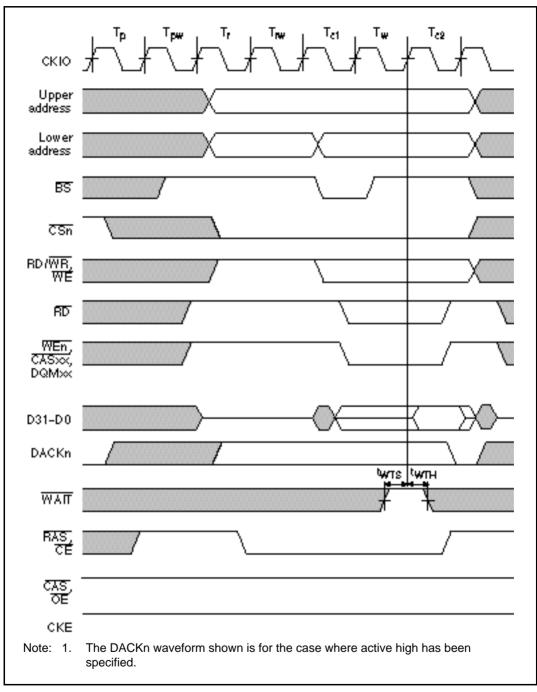

| 7.5 | Synchro | onous DRAM Interface                          | 145 |

|     | 7.5.1   | Synchronous DRAM Direct Connection.           | 145 |

|     | 7.5.2   | Address Multiplex                             | 147 |

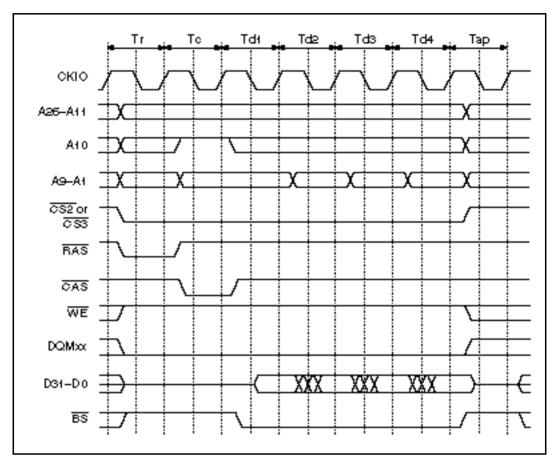

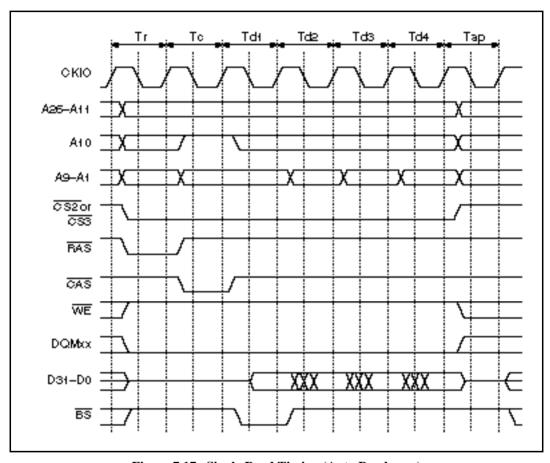

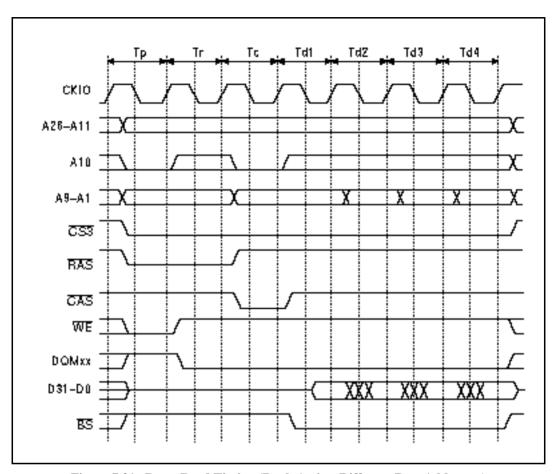

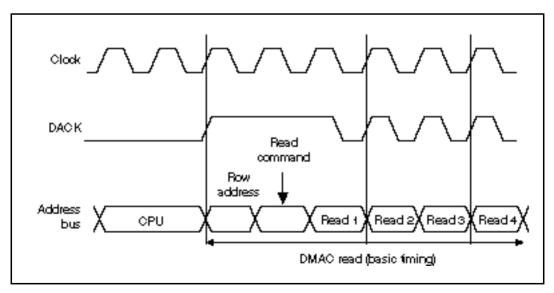

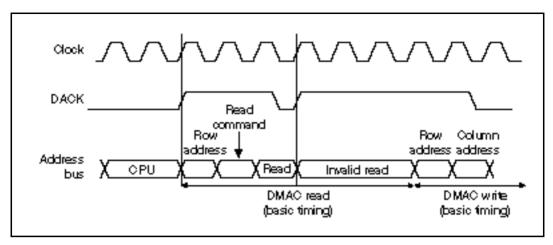

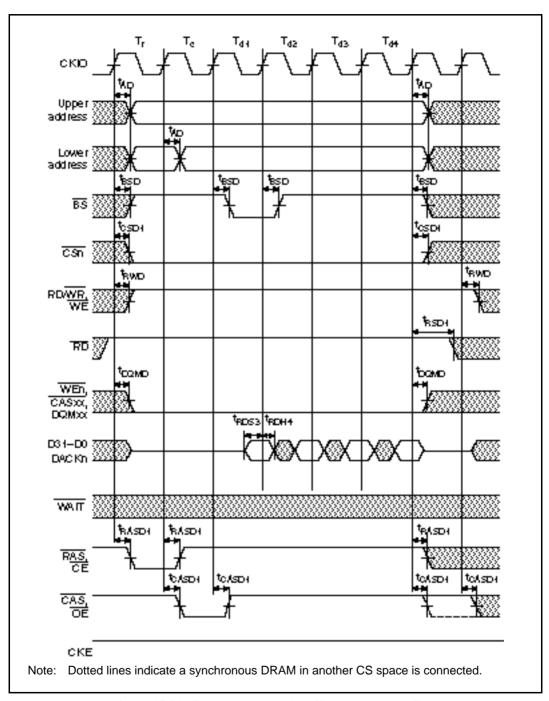

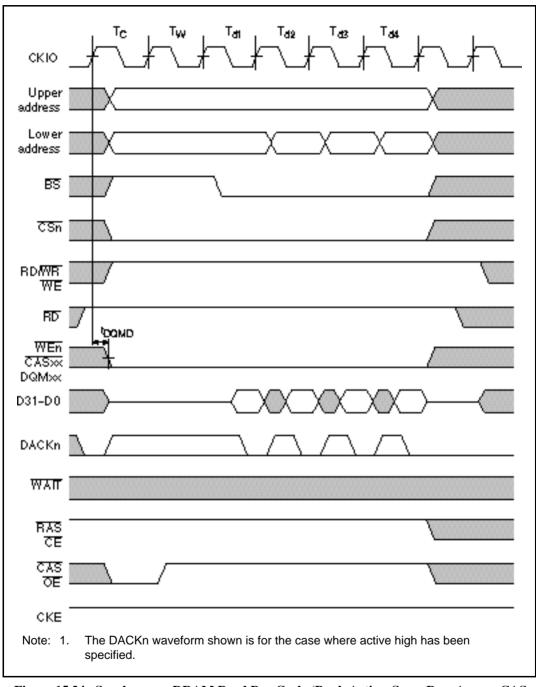

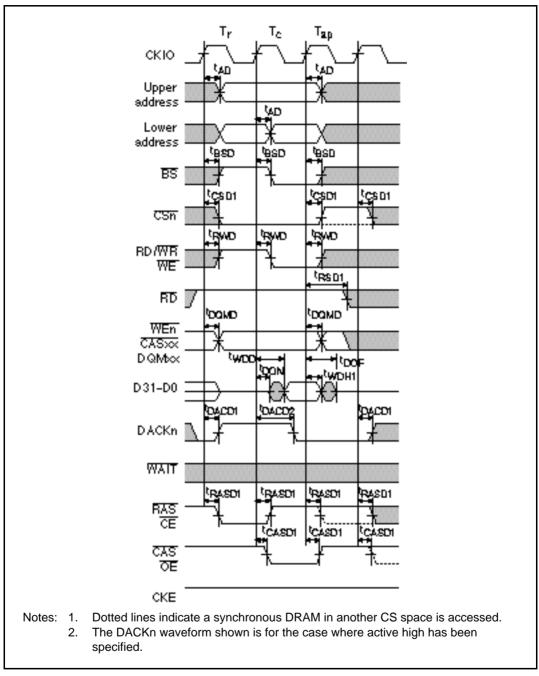

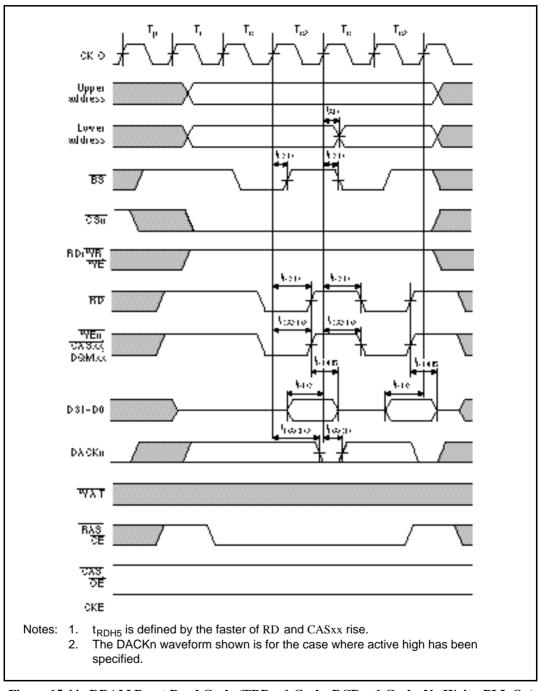

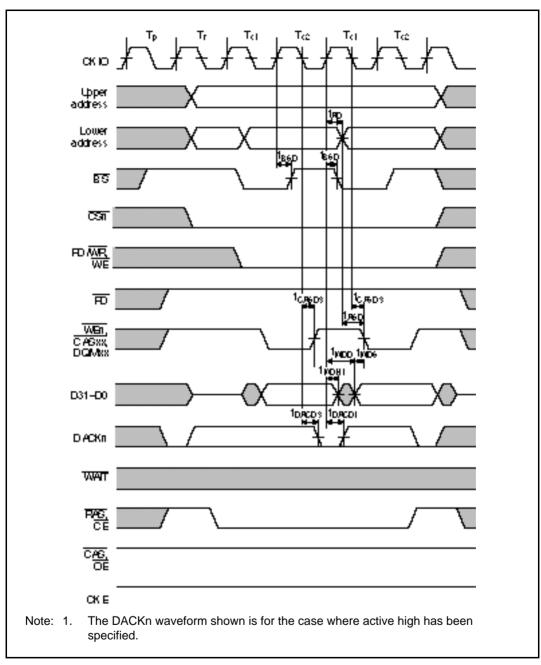

|     | 7.5.3   | Burst Read                                    | 148 |

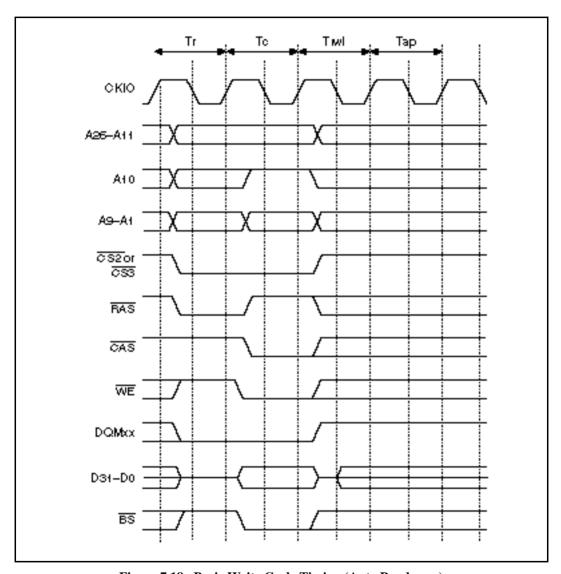

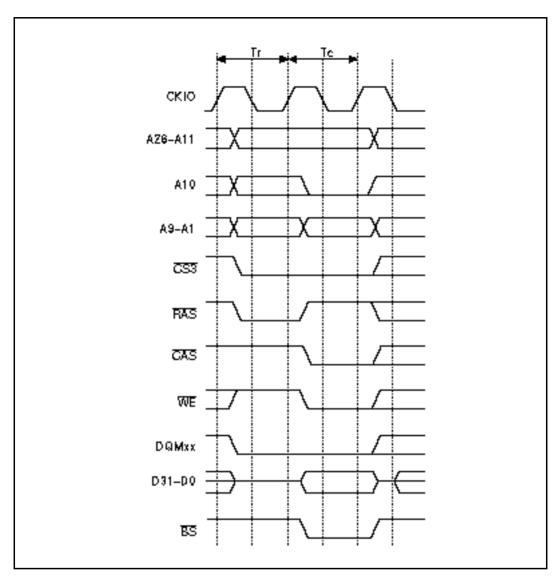

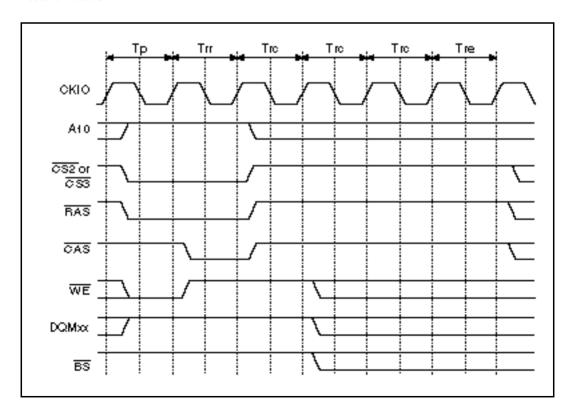

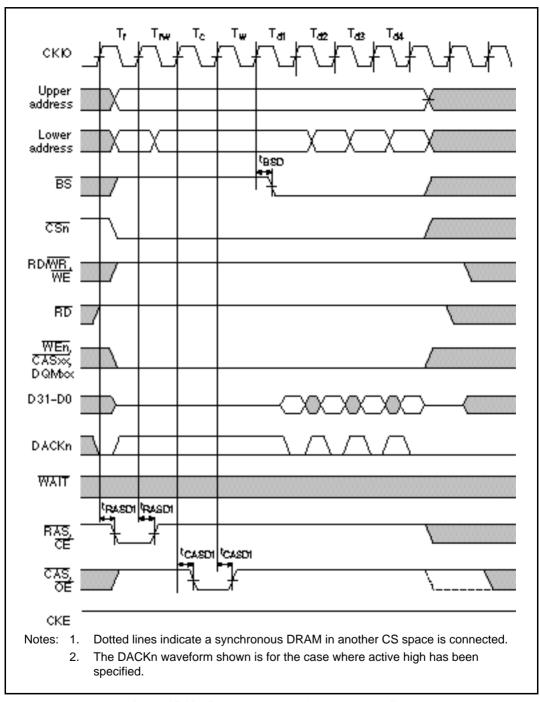

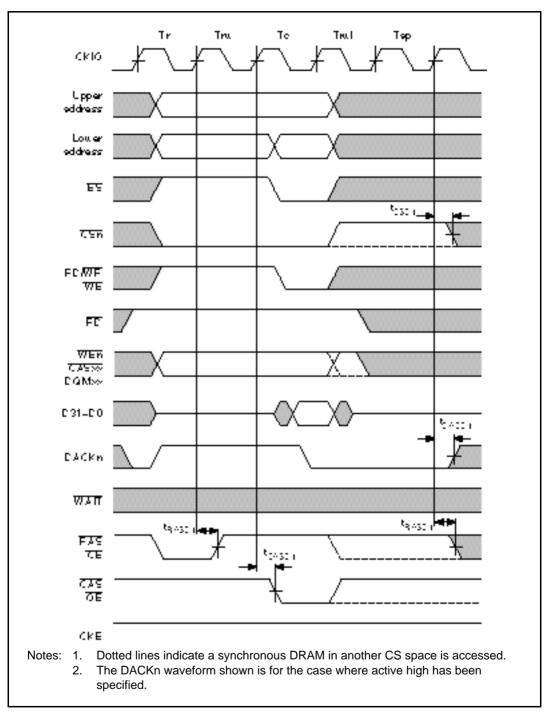

|     | 7.5.4   | Single Read                                   | 151 |

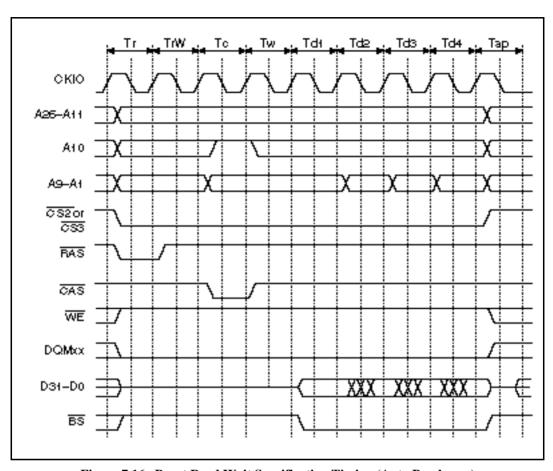

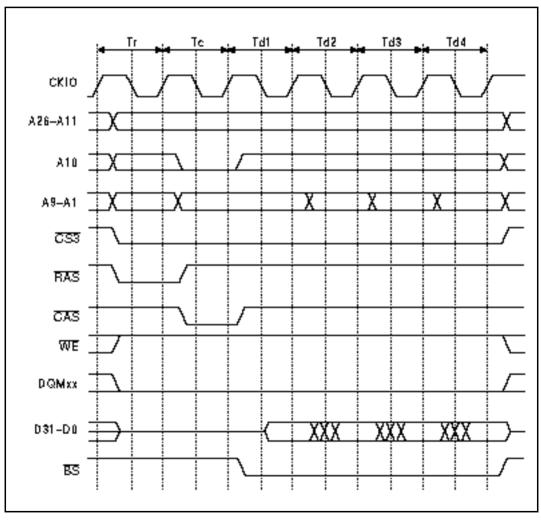

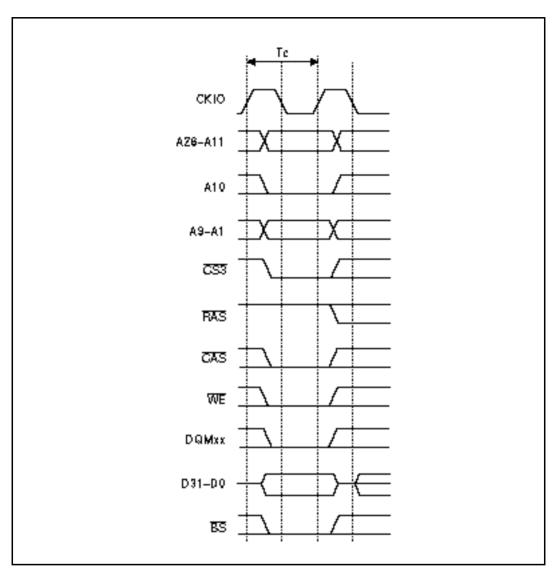

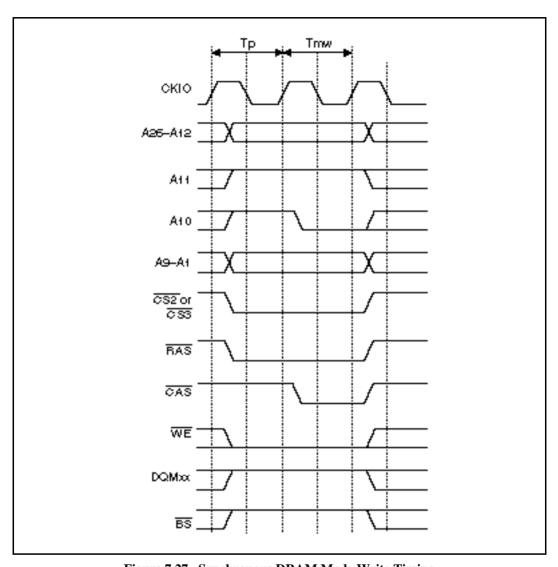

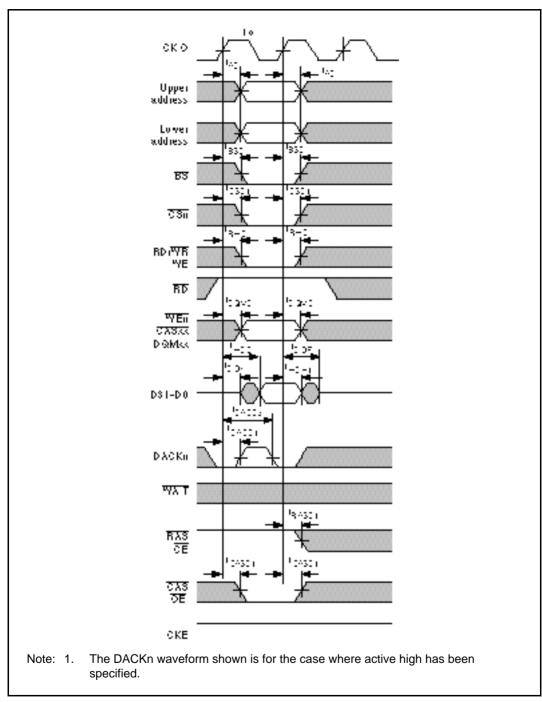

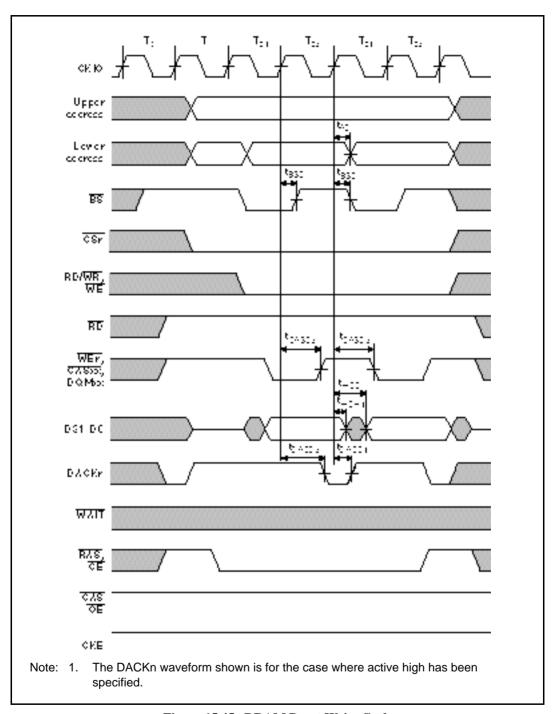

|     | 7.5.5   | Write                                         | 152 |

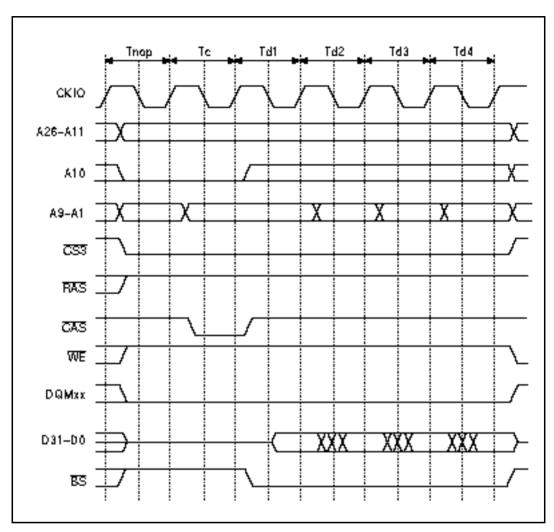

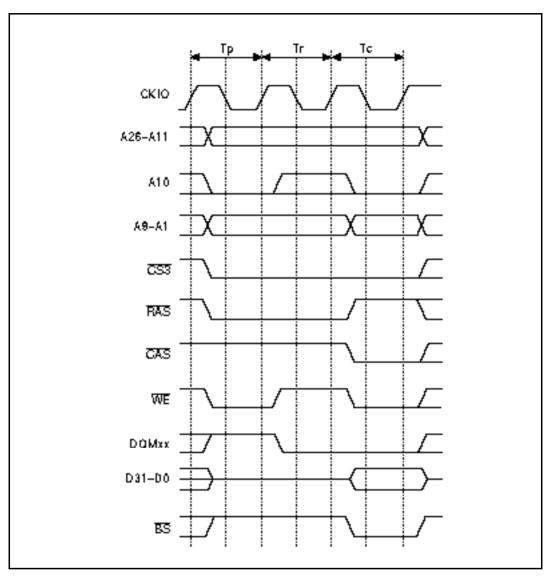

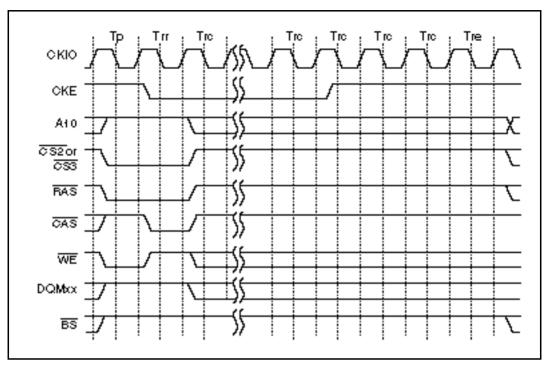

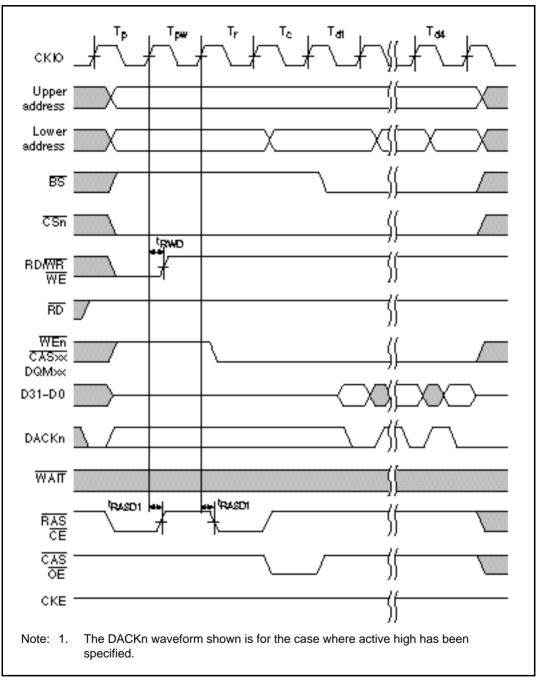

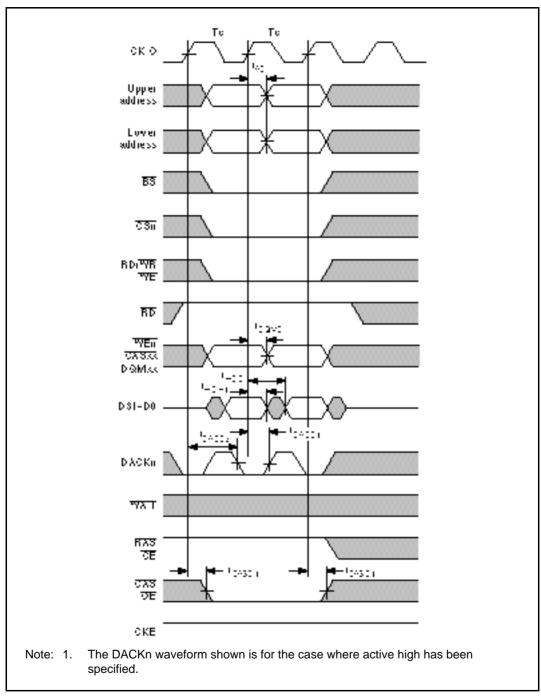

|     | 7.5.6   | Bank Active.                                  | 154 |

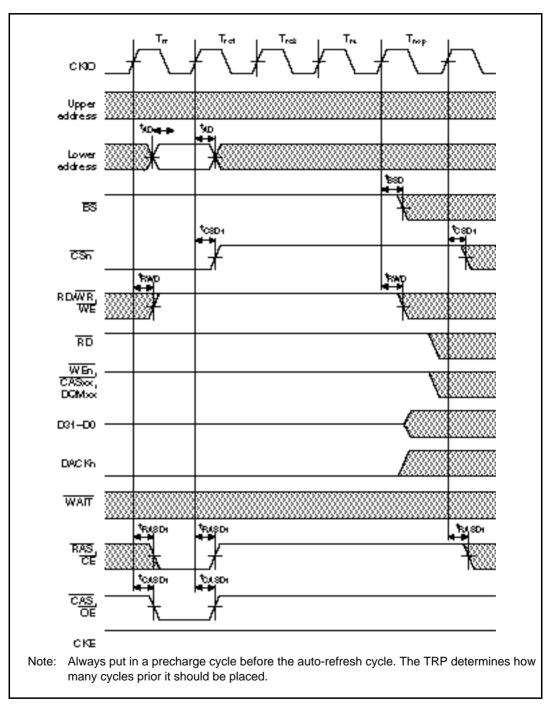

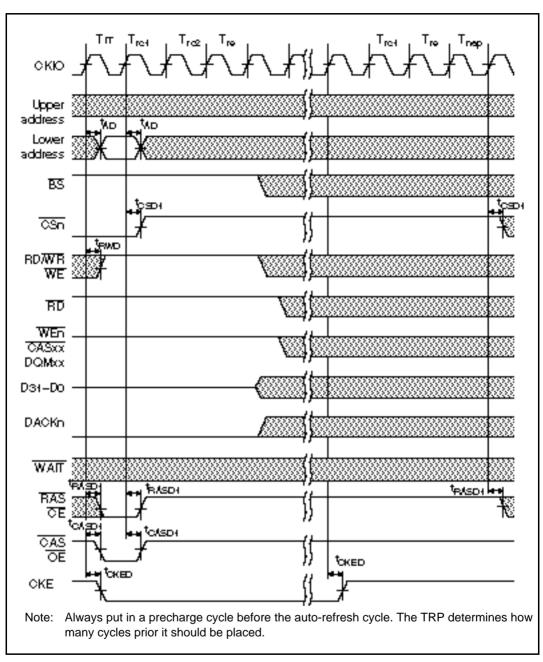

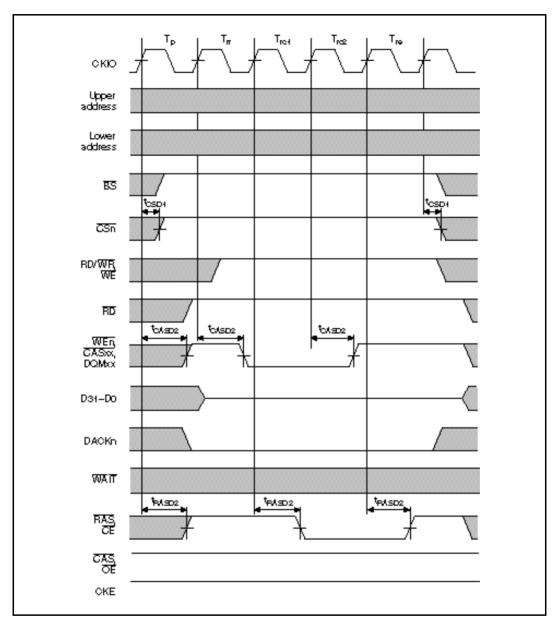

|     | 7.5.7   | Refreshes                                     | 160 |

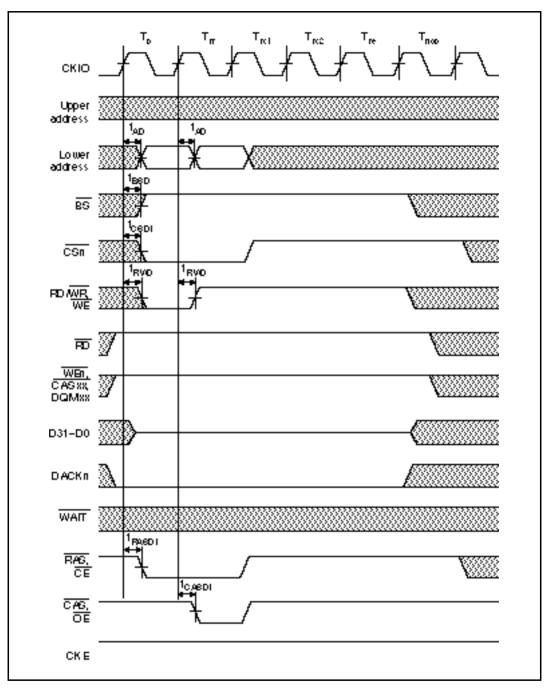

|     | 7.5.8   | Power-On Sequence                             | 163 |

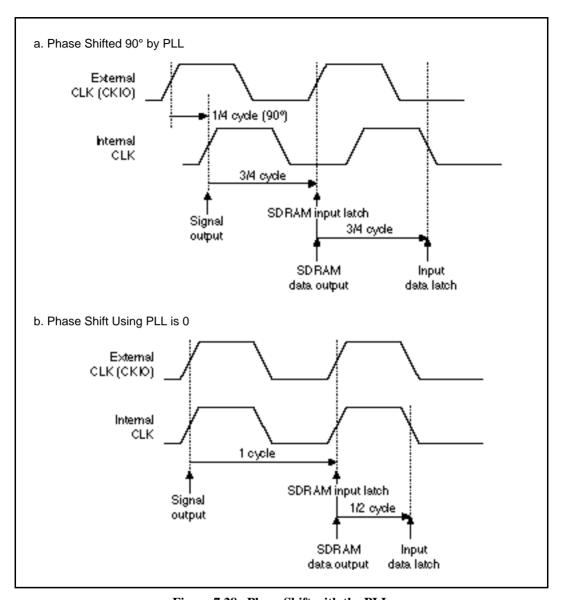

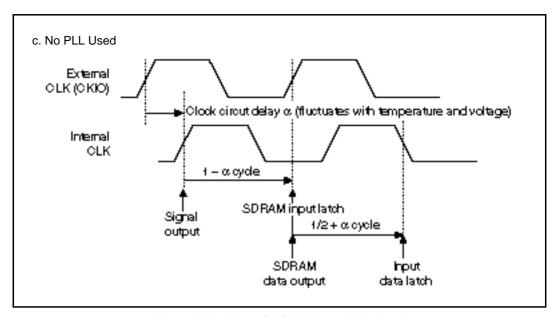

|     | 7.5.9   | Phase Shift by PLL                            | 165 |

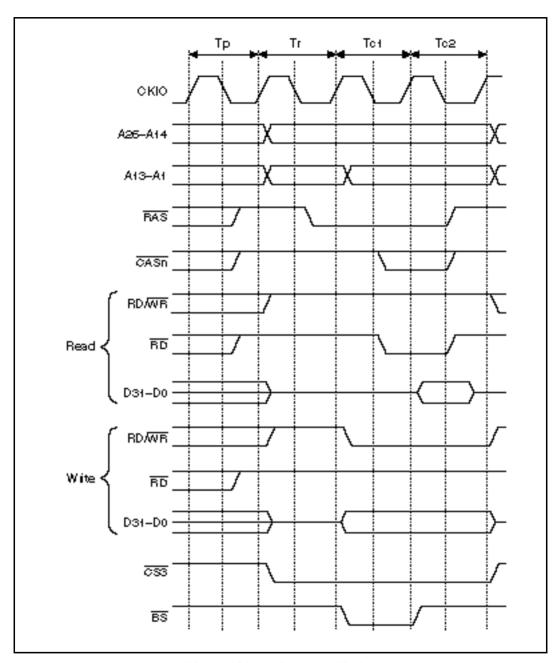

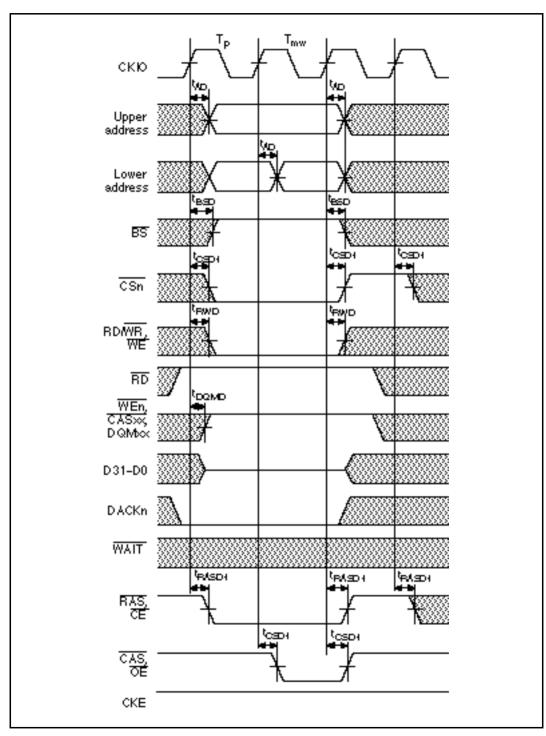

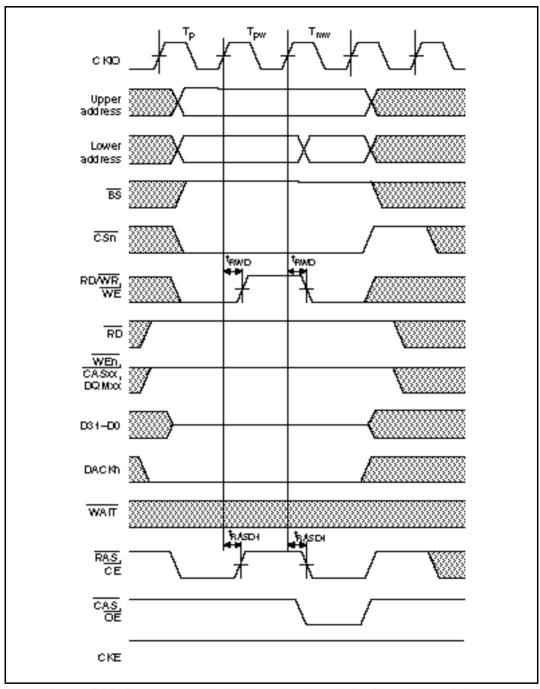

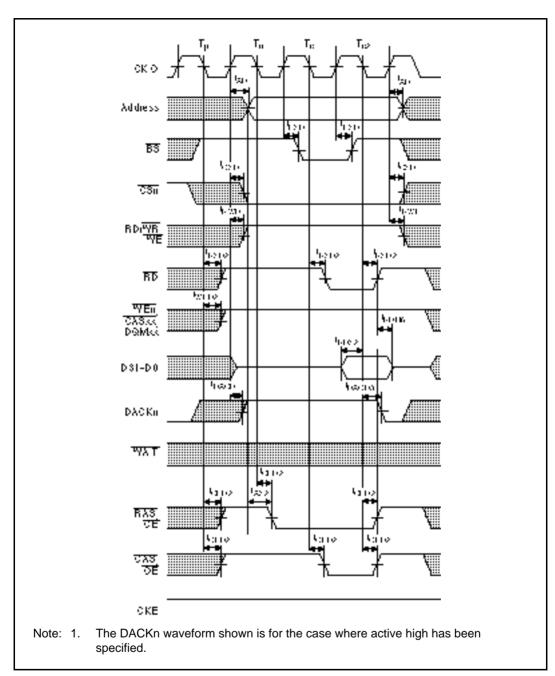

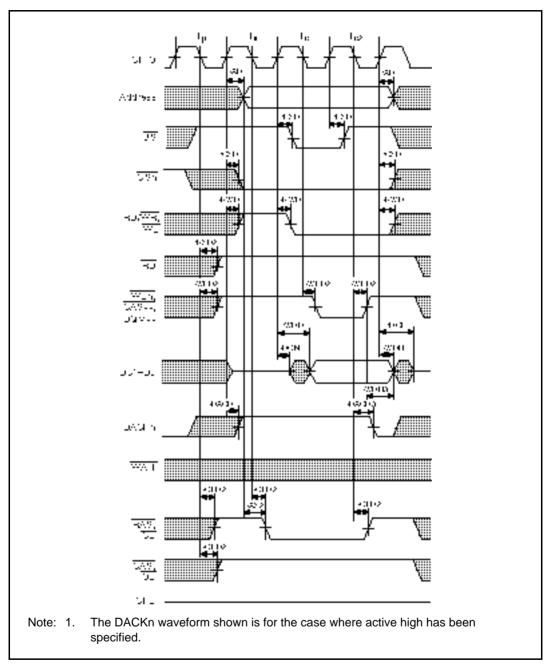

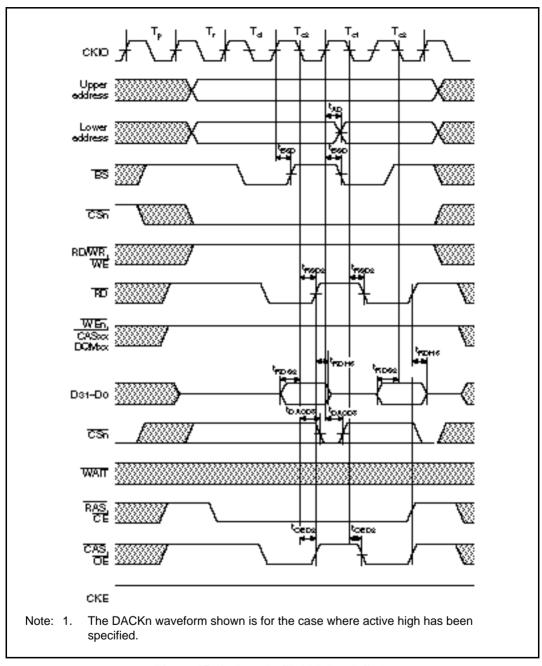

| 7.6 | DRAM    | Interface.                                    | 168 |

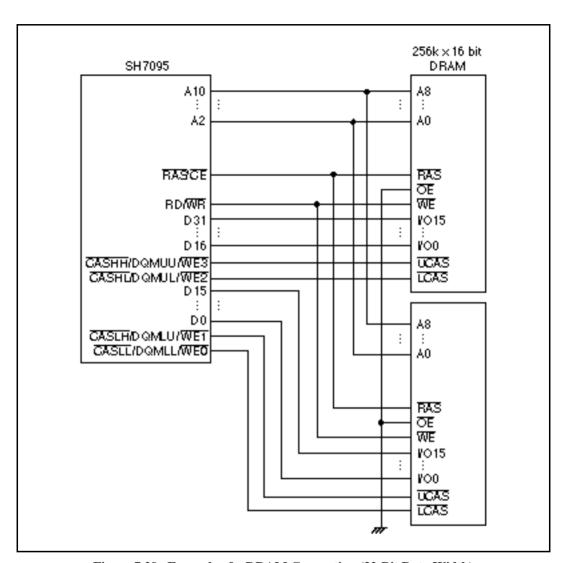

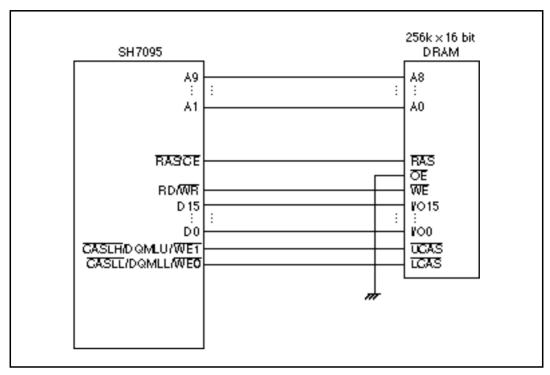

|     | 7.6.1   | DRAM Direct Connection                        | 168 |

|     | 7.6.2   | Address Multiplex                             | 170 |

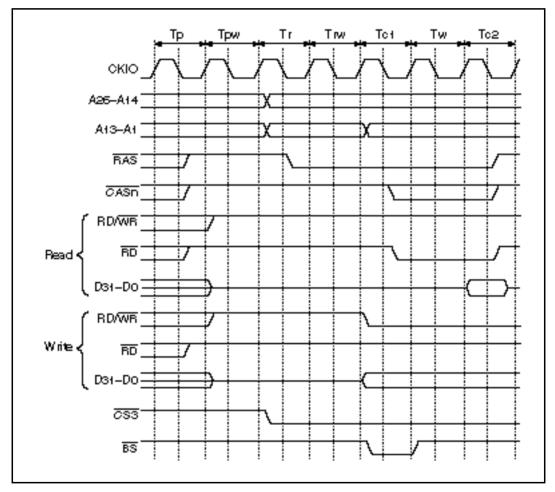

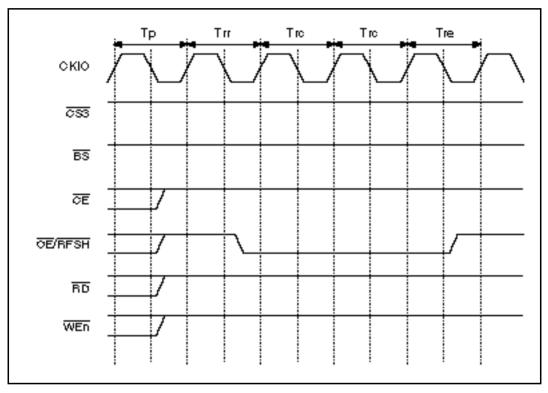

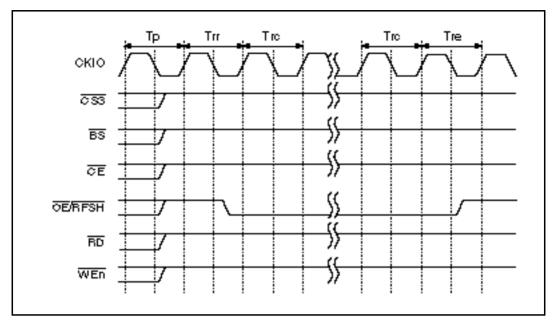

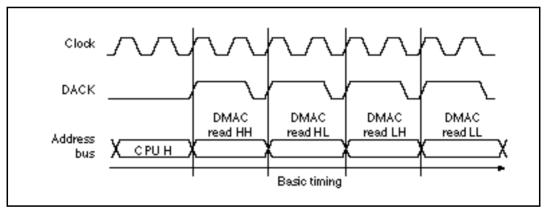

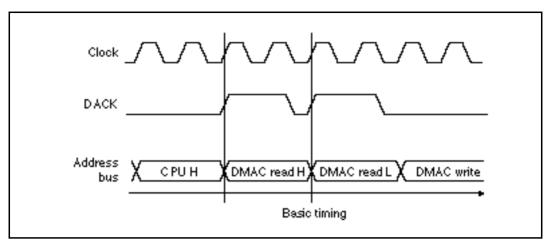

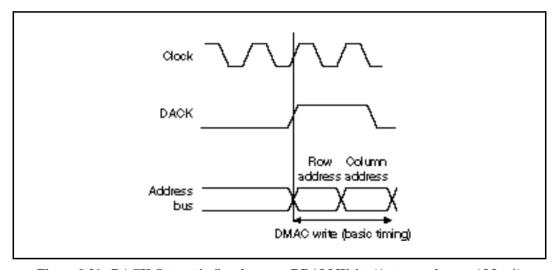

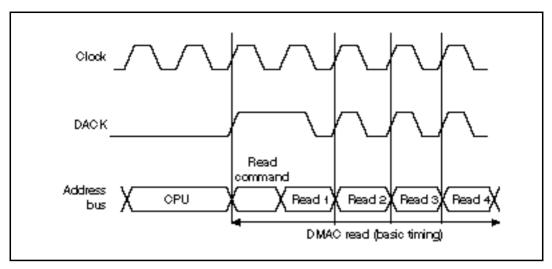

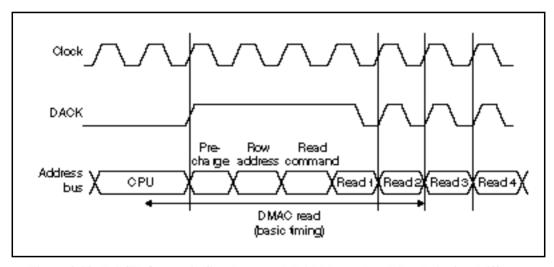

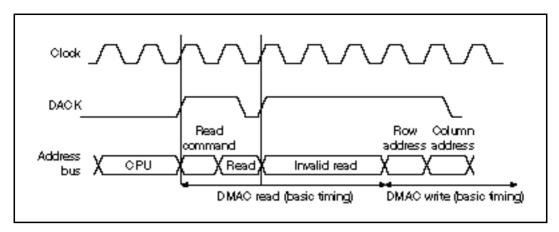

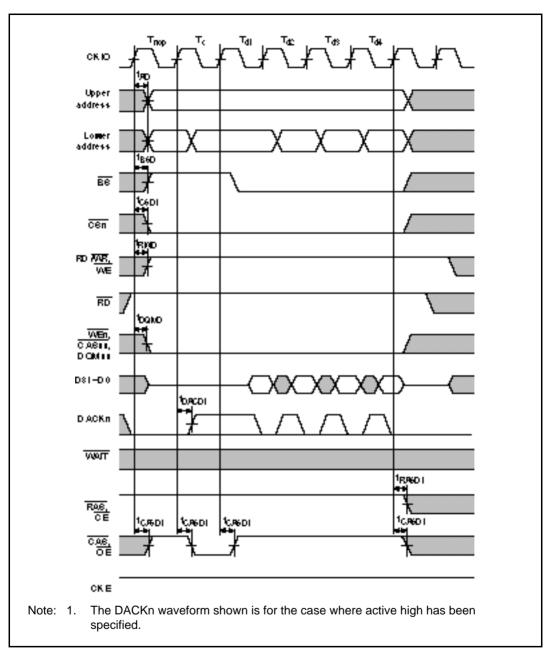

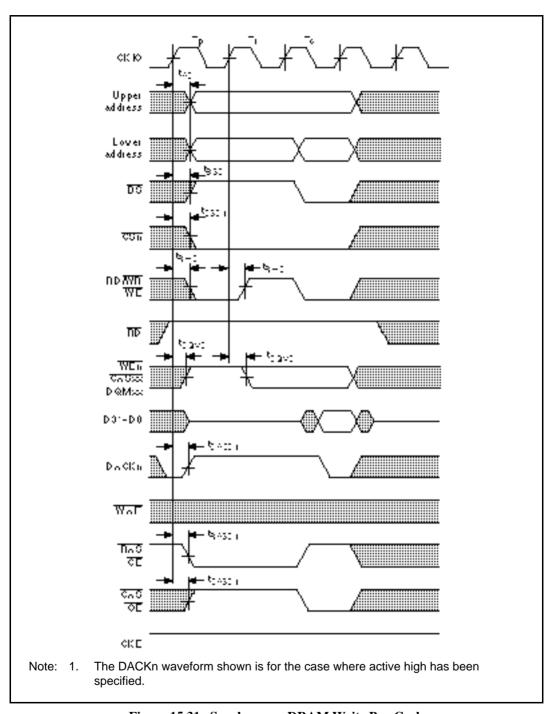

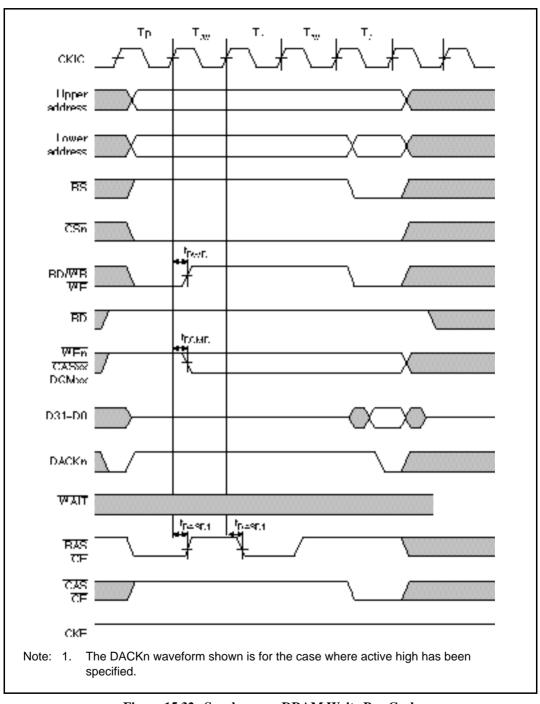

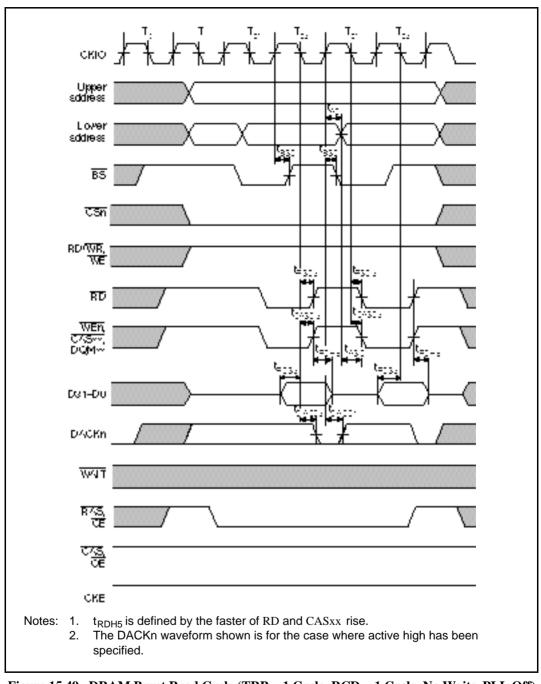

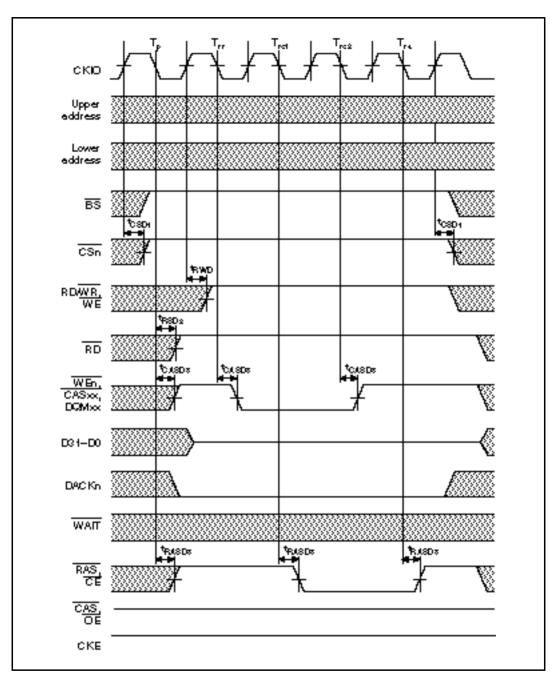

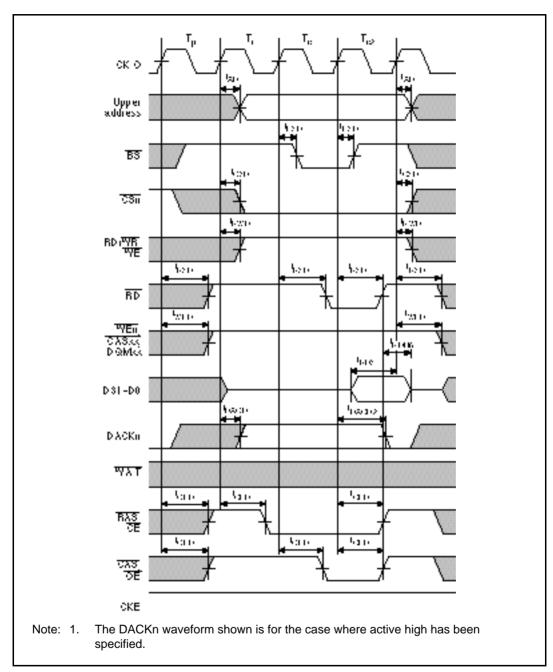

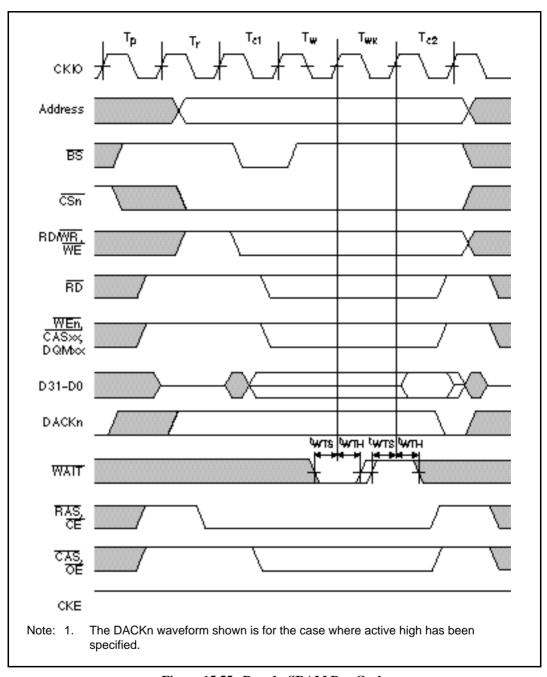

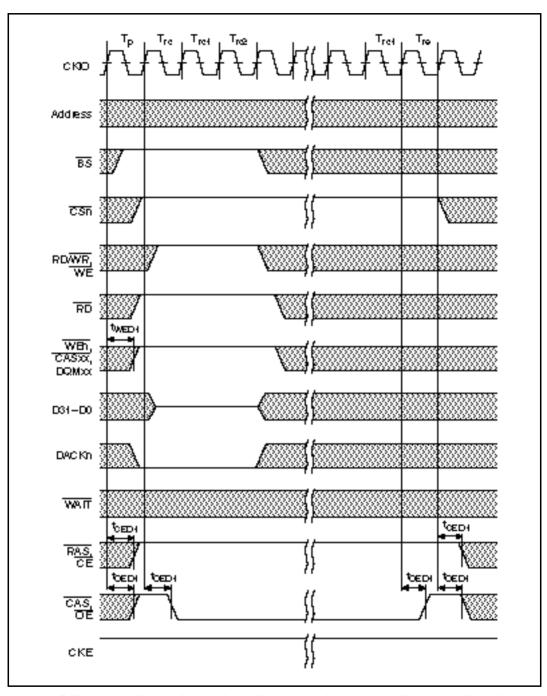

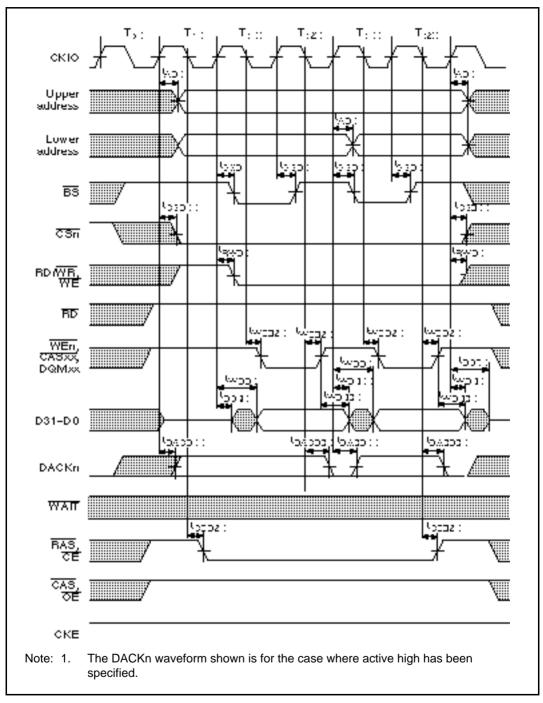

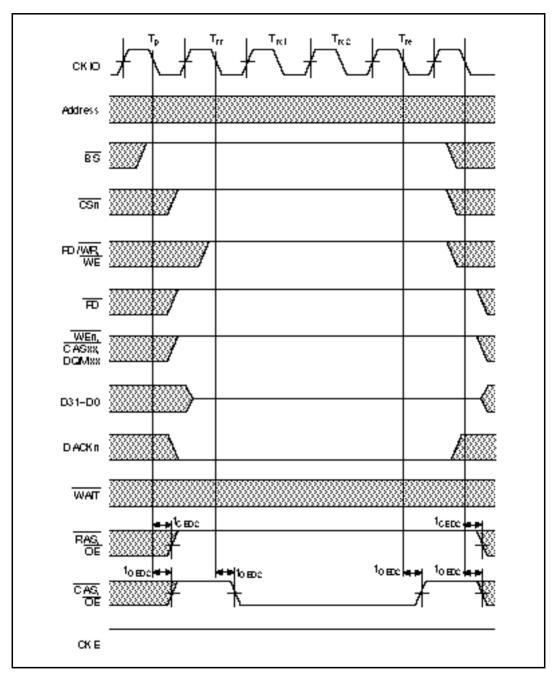

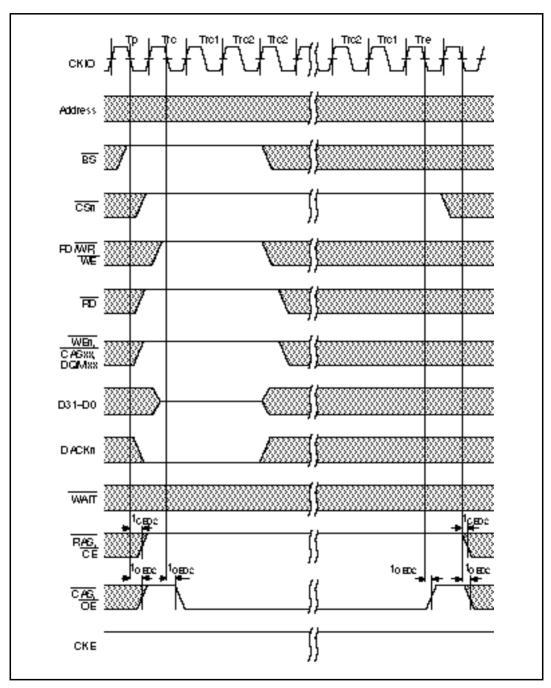

|     | 7.6.3   | Basic Timing                                  | 171 |

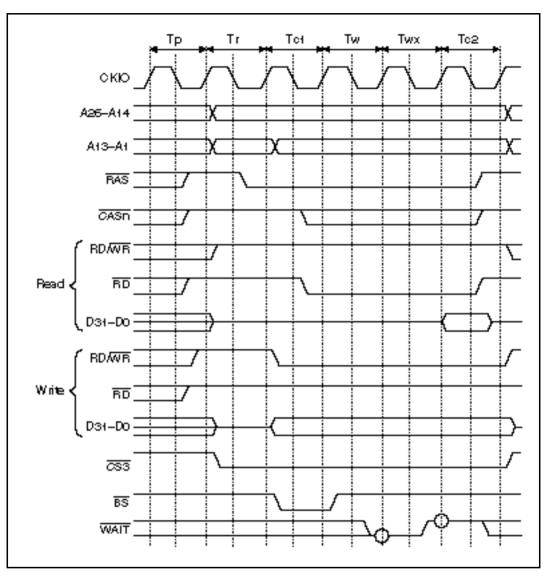

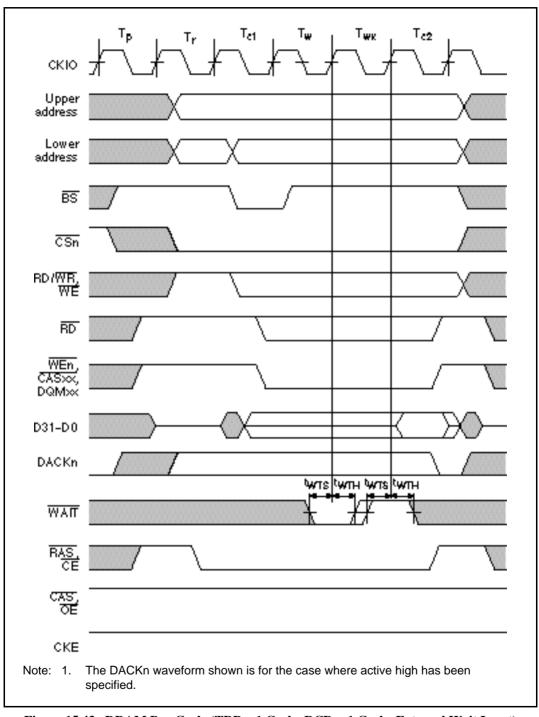

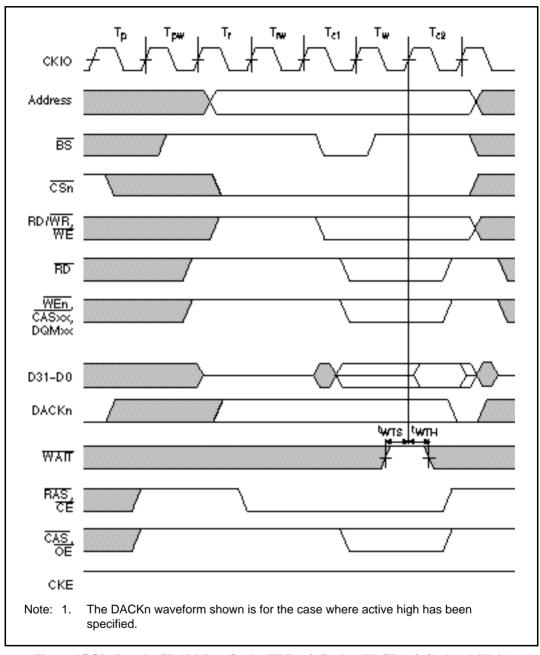

|     | 7.6.4   | Wait State Control                            | 172 |

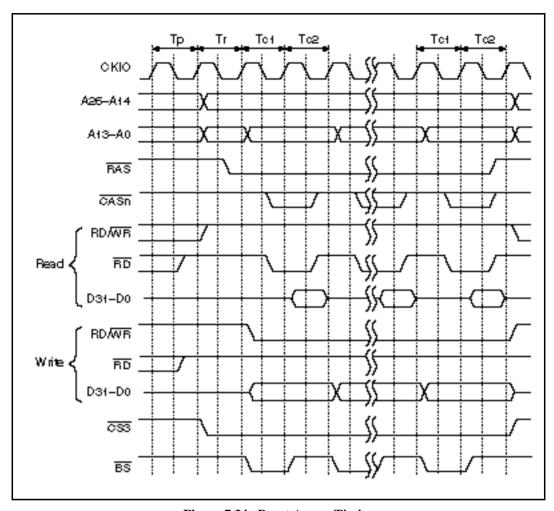

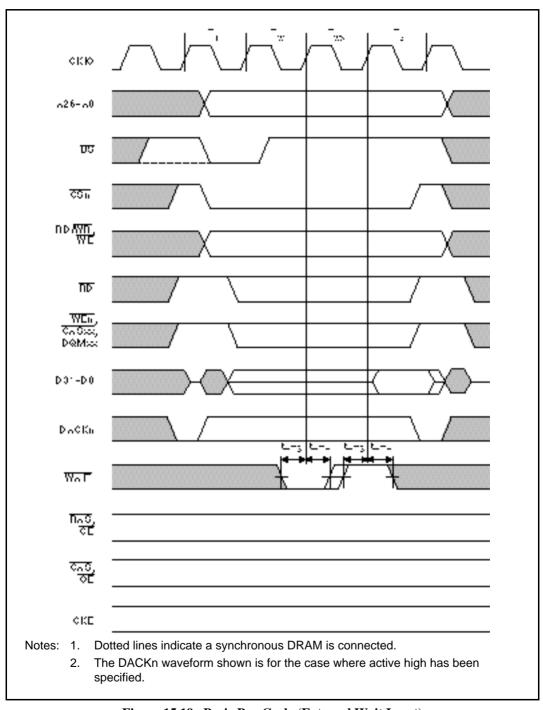

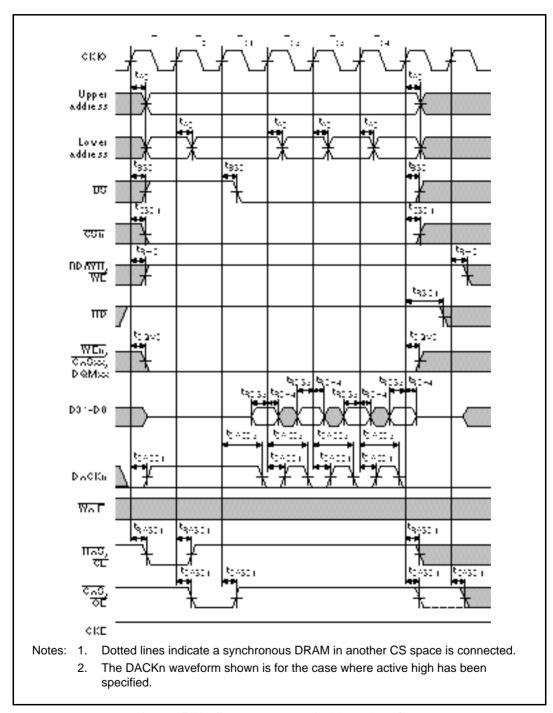

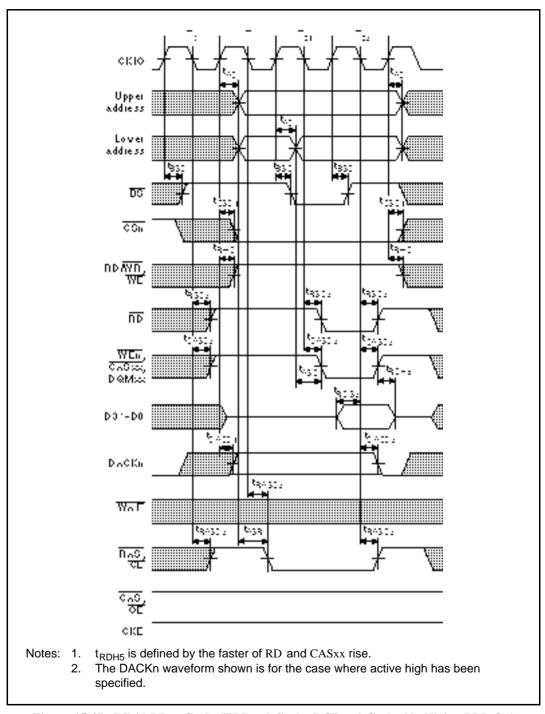

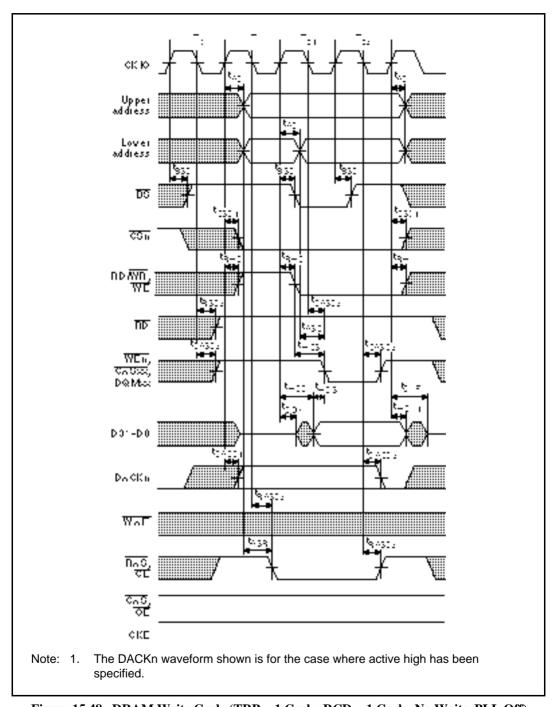

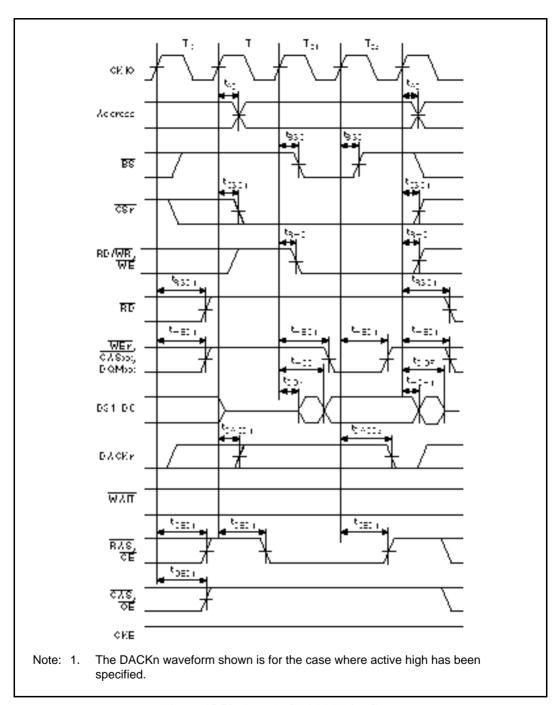

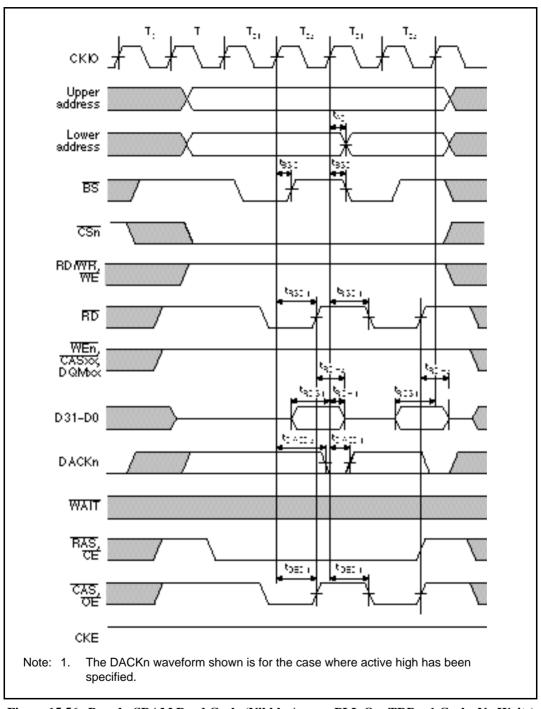

|     | 7.6.5   | Burst Access                                  | 174 |

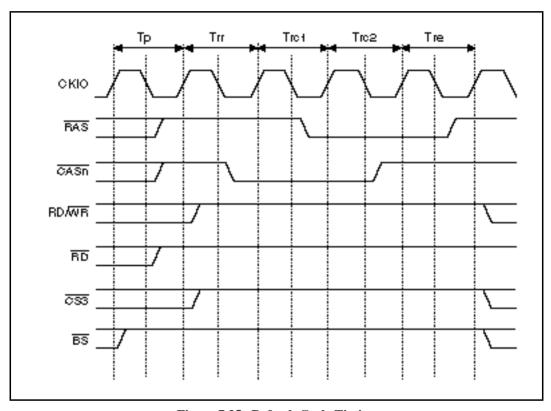

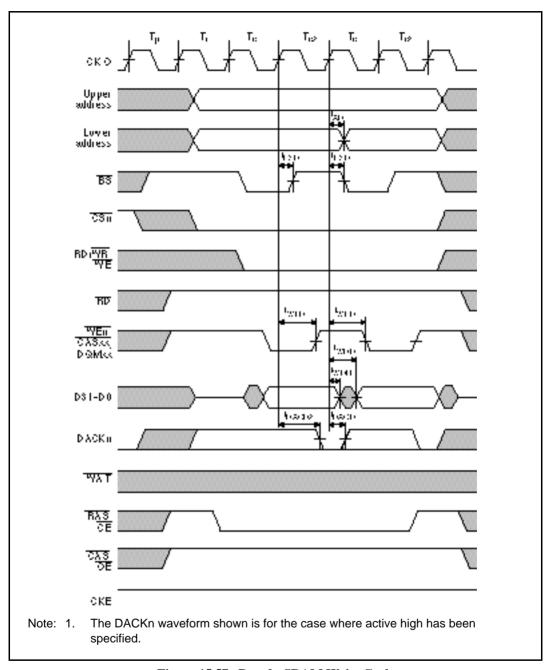

|     | 7.6.6   | Refresh Timing                                | 176 |

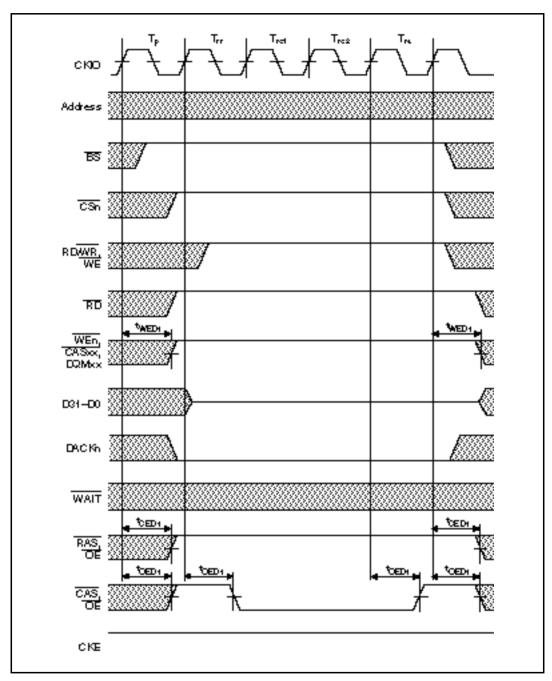

|     | 7.6.7   | Power-On Sequence                             | 177 |

| 7.7 | Pseudo- | -SRAM Interface                               |     |

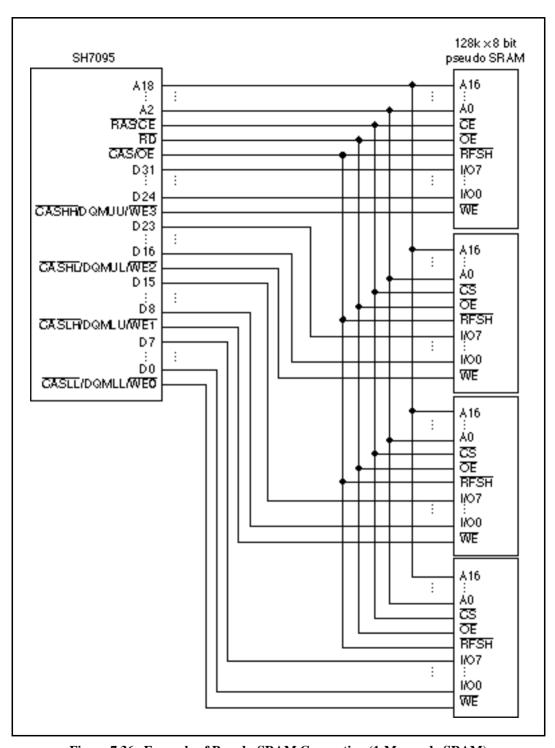

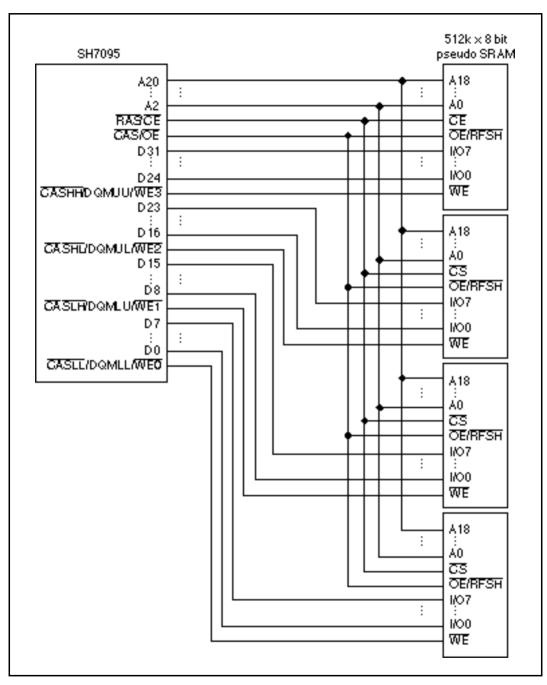

|     | 7.7.1   | Pseudo-SRAM Direct Connection.                | 178 |

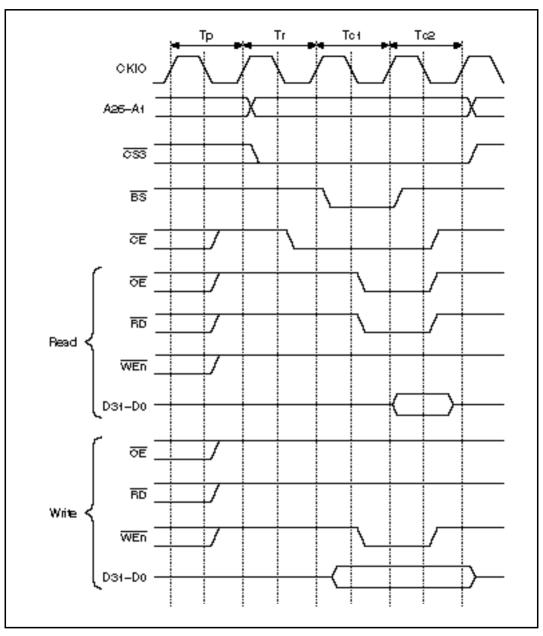

|     | 7.7.2   | Basic Timing                                  | 181 |

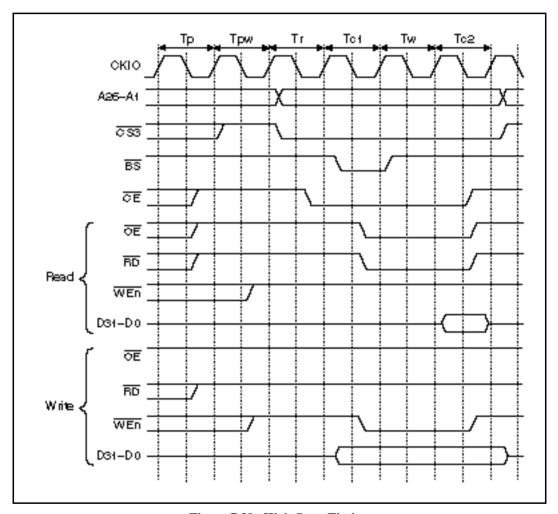

|     | 7.7.3   | Wait State Control                            | 182 |

|     | 7.7.4   | Burst Access                                  | 184 |

|     | 7.7.5   | Refresh                                       |     |

|     | 7.7.6   | Power-On Sequence                             |     |

| 7.8 | Burst R | OM Interface                                  | 187 |

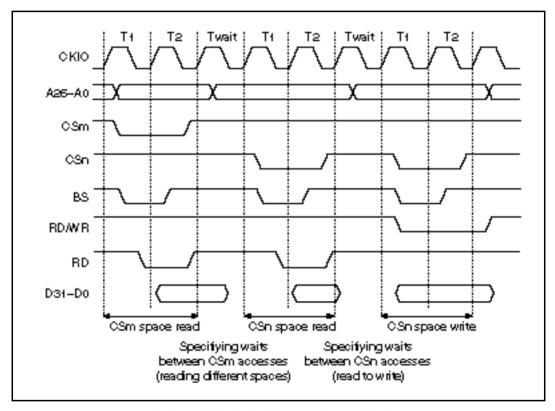

| 7.9  | Waits b | petween Access Cycles                                     | 190 |

|------|---------|-----------------------------------------------------------|-----|

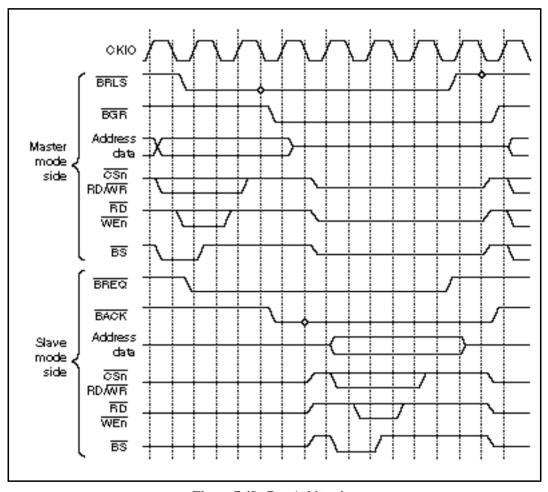

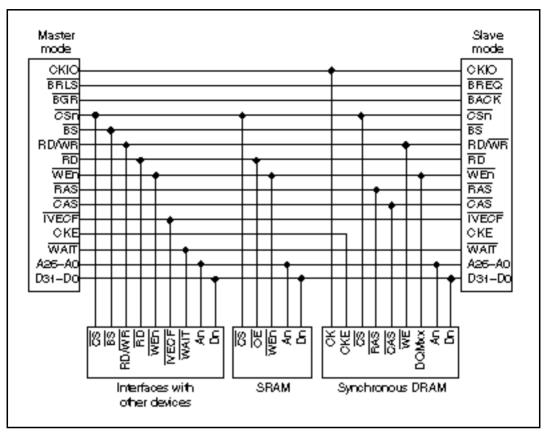

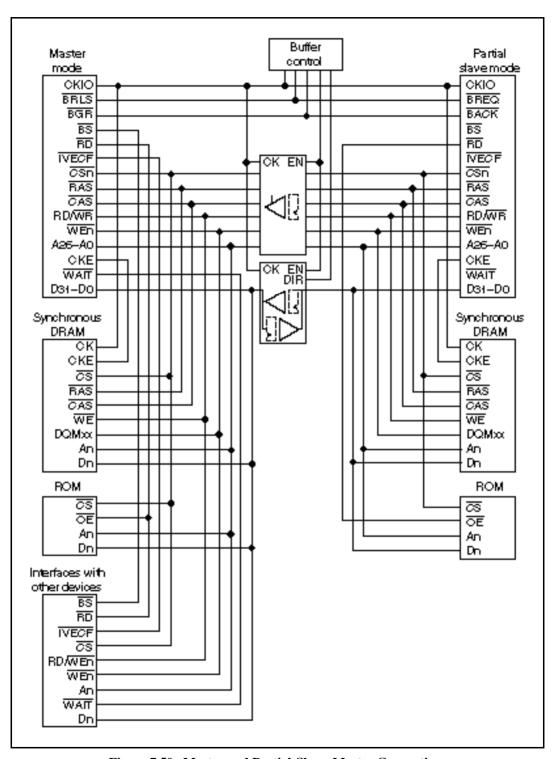

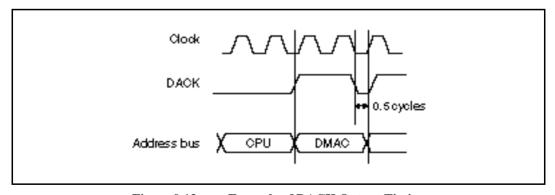

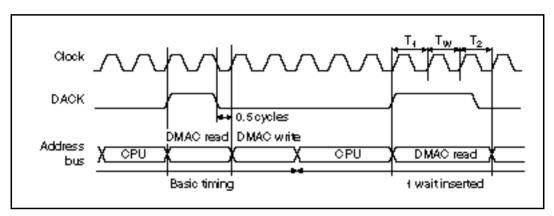

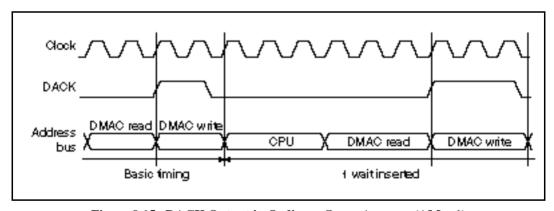

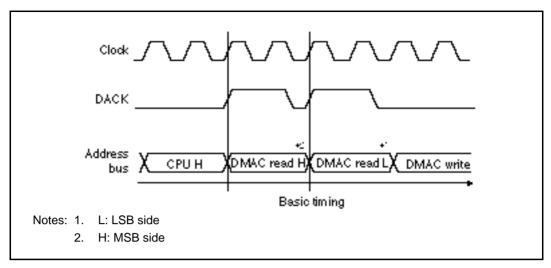

| 7.10 | Bus Ar  | bitration                                                 | 191 |

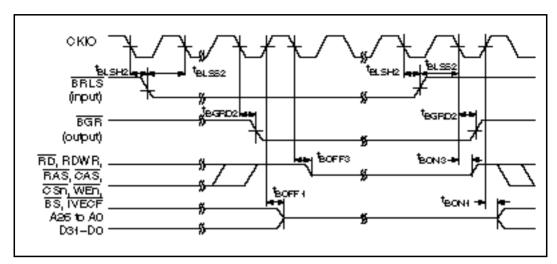

|      | 7.10.1  | Master Mode                                               | 193 |

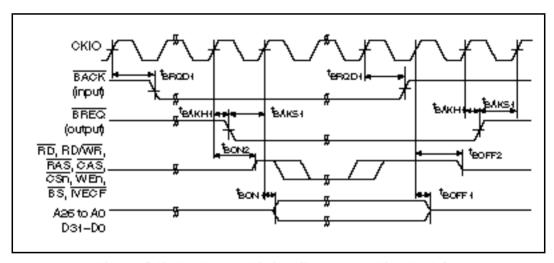

|      | 7.10.2  | Slave Mode                                                | 195 |

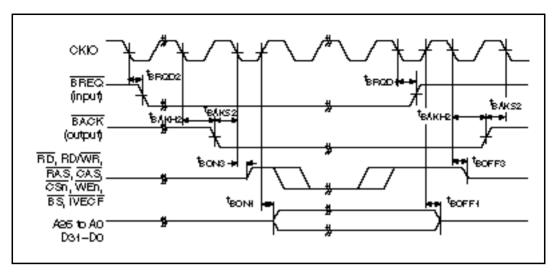

|      | 7.10.3  | Partial-Share Master Mode                                 | 196 |

|      | 7.10.4  | External Bus Address Monitor                              | 199 |

|      | 7.10.5  | Master and Slave Coordination                             | 199 |

| 7.11 | Other 7 | Горісs                                                    | 200 |

|      |         | Resets                                                    |     |

|      | 7.11.2  | Access as Seen from the CPU or DMAC                       | 200 |

|      | 7.11.3  | Emulator                                                  | 202 |

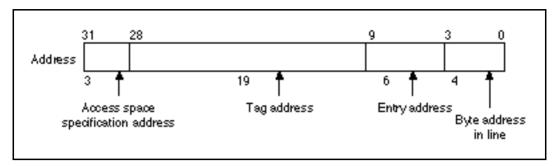

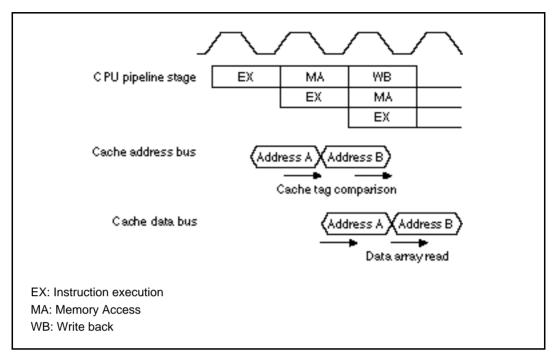

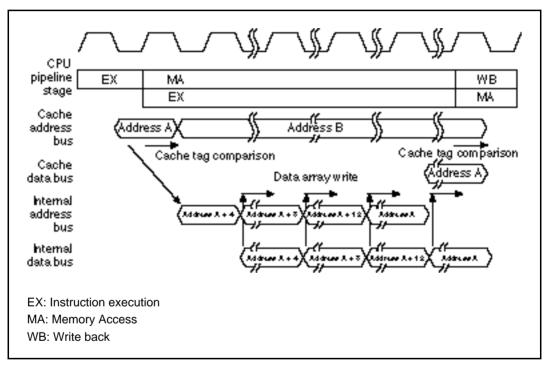

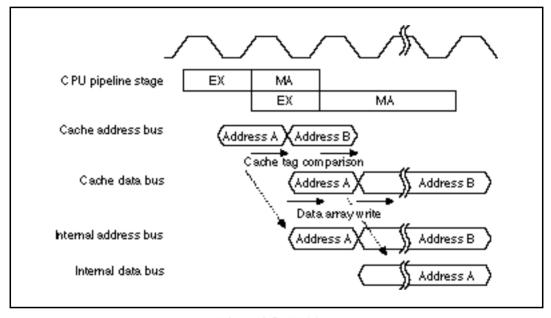

| Sect | ion 8   | Cache                                                     | 203 |

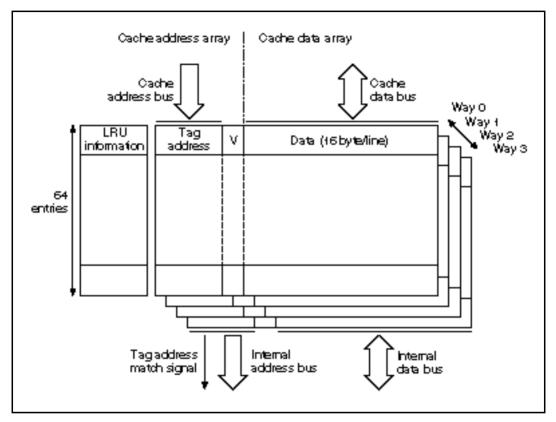

| 8.1  | Introdu | oction                                                    | 203 |

| 8.2  | Cache   | Control Register (CCR)                                    | 204 |

| 8.3  | Addres  | s Space and the Cache                                     | 205 |

| 8.4  | Cache   | Operation                                                 | 206 |

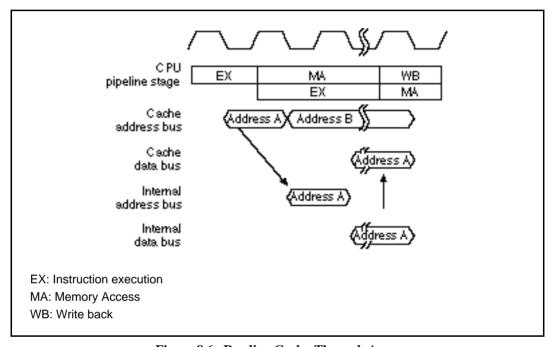

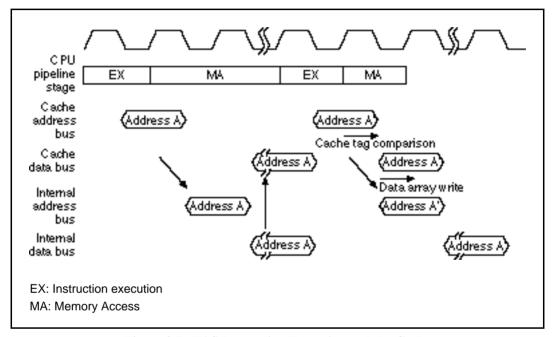

|      | 8.4.1   | Cache Reads                                               | 206 |

|      | 8.4.2   | Writing                                                   | 209 |

|      | 8.4.3   | Cache-Through Access.                                     | 210 |

|      | 8.4.4   | The TAS Instruction                                       | 211 |

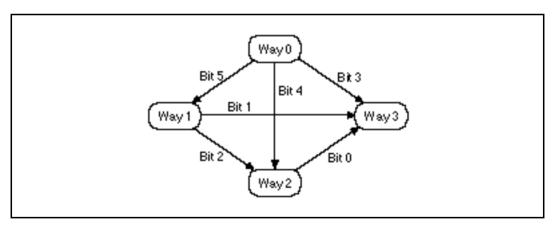

|      | 8.4.5   | Pseudo LRU and Cache Replacement                          | 211 |

|      | 8.4.6   | Cache Initialization                                      | 213 |

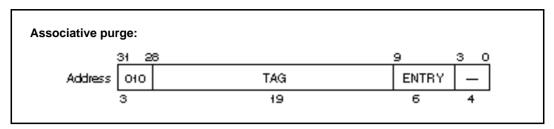

|      | 8.4.7   | Associative Purges.                                       | 213 |

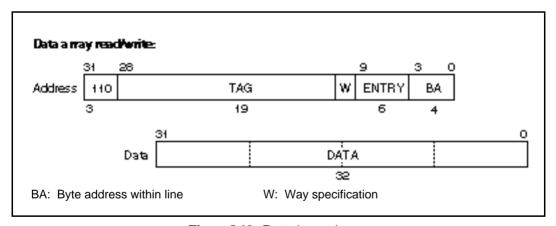

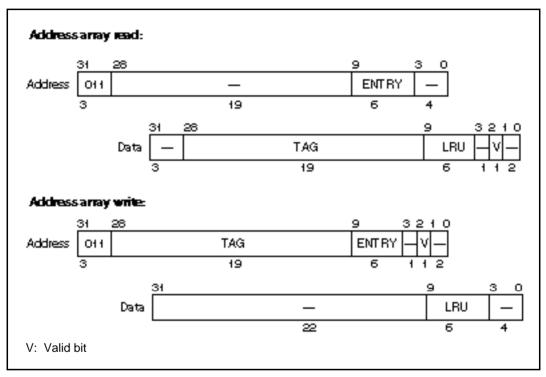

|      | 8.4.8   | Data Array Access                                         | 214 |

|      | 8.4.9   | Address Array Access                                      | 214 |

| 8.5  | Cache   | Use                                                       | 215 |

|      | 8.5.1   | Initialization                                            | 215 |

|      | 8.5.2   | Purge of Specific Lines.                                  | 216 |

|      | 8.5.3   | Cache Data Coherency                                      | 217 |

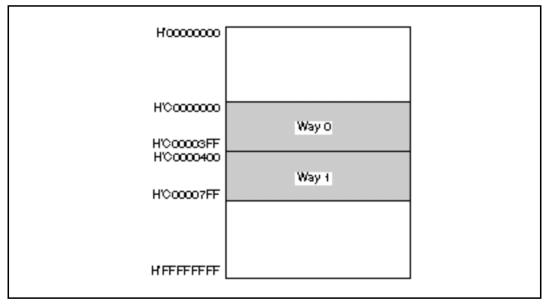

|      | 8.5.4   | Two-Way Cache Mode                                        | 218 |

|      | 8.5.5   | Usage Notes                                               | 218 |

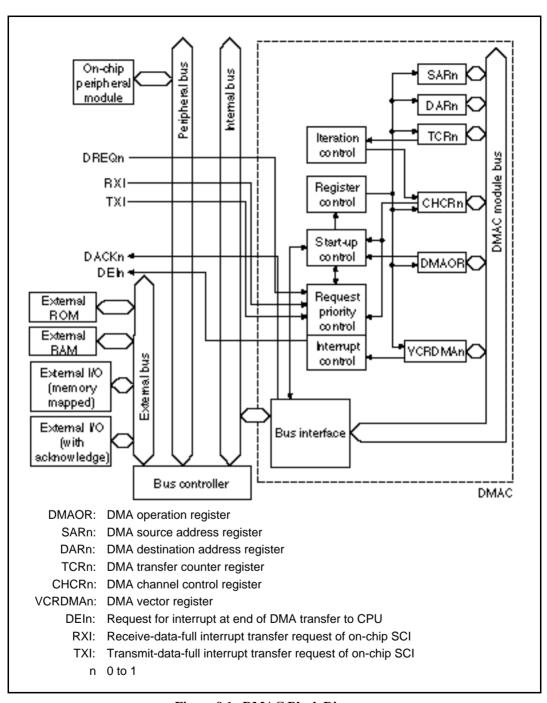

| Sect | ion 9   | Direct Memory Access Controller (DMAC)                    | 221 |

|      | Overvi  |                                                           | 221 |

|      | 9.1.1   | Features                                                  | 221 |

|      | 9.1.2   | Block Diagram                                             |     |

|      | 9.1.3   | Pin Configuration                                         |     |

|      | 9.1.4   | Register Configuration                                    | 224 |

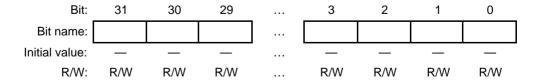

| 9.2  | Registe | er Descriptions                                           |     |

|      | 9.2.1   | DMA Source Address Registers 0 and 1 (SAR0 and SAR1)      |     |

|      | 9.2.2   | DMA Destination Address Registers 0 and 1 (DAR0 and DAR1) |     |

|      | 9.2.3   | DMA Transfer Count Registers 0 and 1 (TCR0 and TCR1)      | 226 |

|      | 9.2.4   | DMA Channel Control Registers 0 and 1 (CHCR0 and CHCR1)  | 227 |

|------|---------|----------------------------------------------------------|-----|

|      | 9.2.5   | DMA Vector Number Registers 0 and 1 (VCRDMA0, VCRDMA1)   | 231 |

|      | 9.2.6   | DMA Request/Response Selection Control Registers 0 and 1 |     |

|      |         | (DRCR0, DRCR1)                                           | 232 |

|      | 9.2.7   | DMA Operation Register (DMAOR)                           | 233 |

| 9.3  | Operati | on                                                       | 234 |

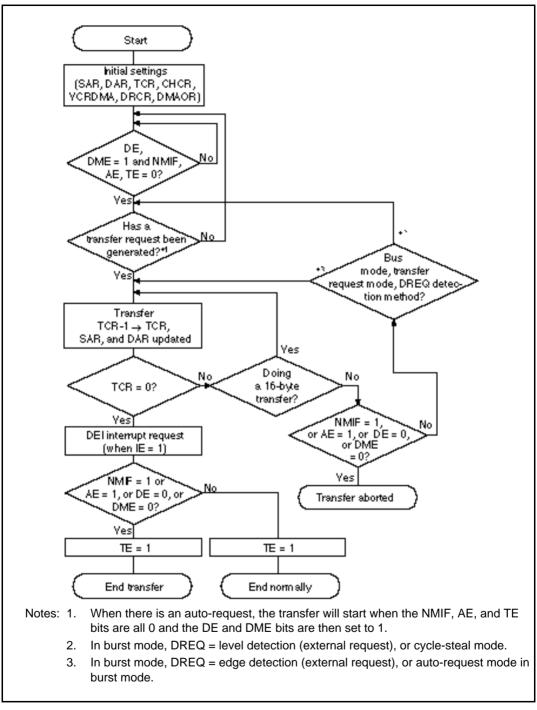

|      | 9.3.1   | DMA Transfer Flow.                                       | 235 |

|      | 9.3.2   | DMA Transfer Requests                                    | 237 |

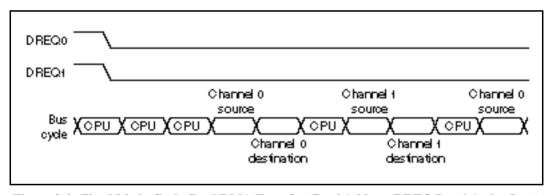

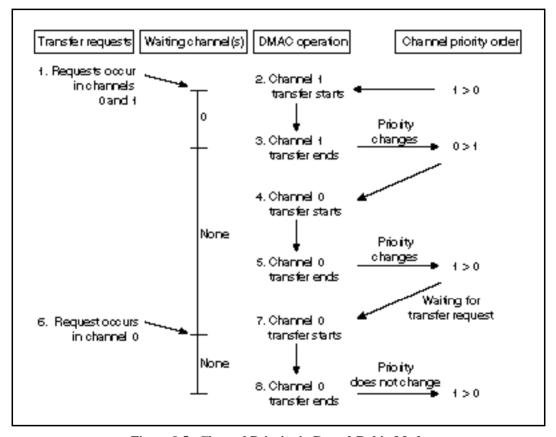

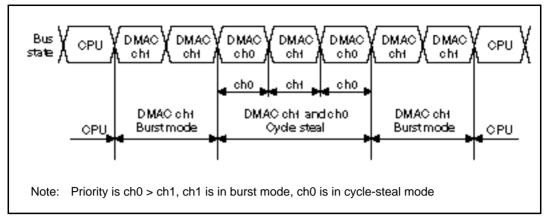

|      | 9.3.3   | Channel Priority                                         | 239 |

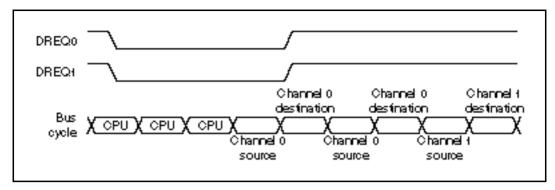

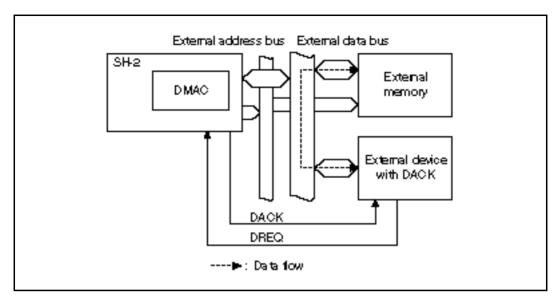

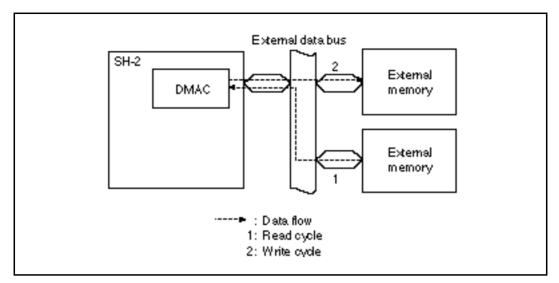

|      | 9.3.4   | DMA Transfer Types                                       | 241 |

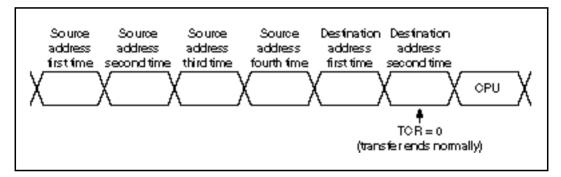

|      | 9.3.5   | Number of Bus Cycles                                     | 249 |

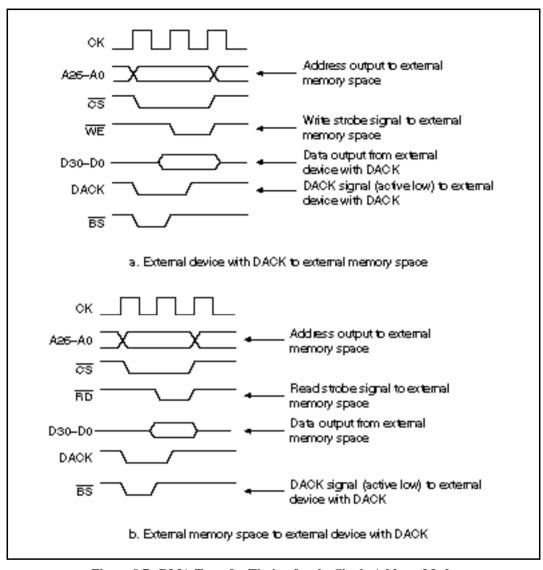

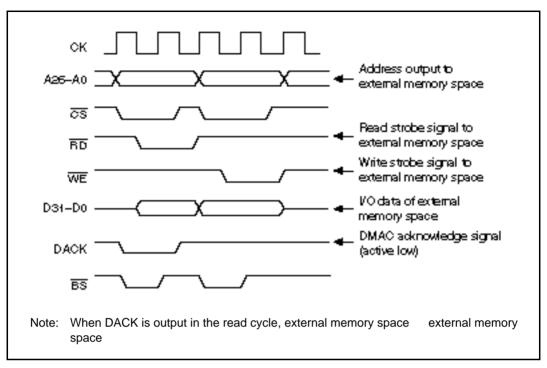

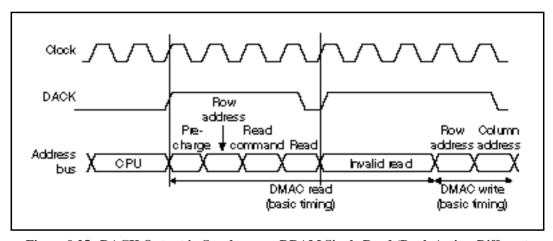

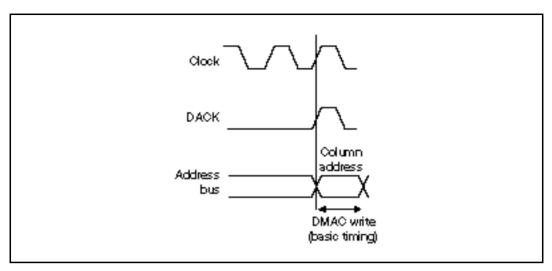

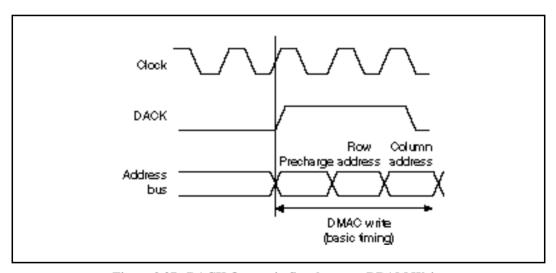

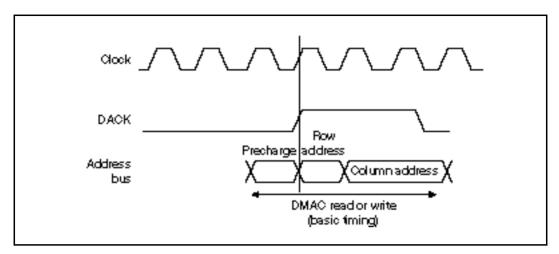

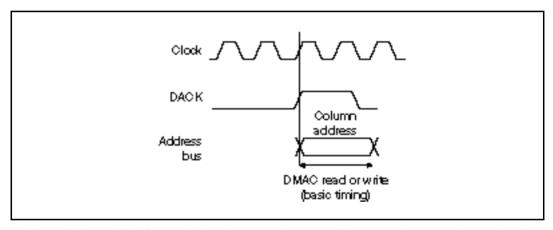

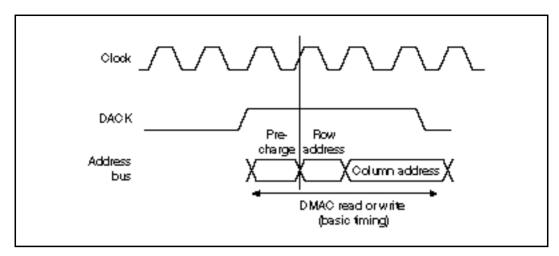

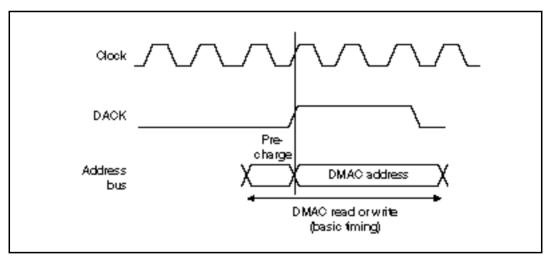

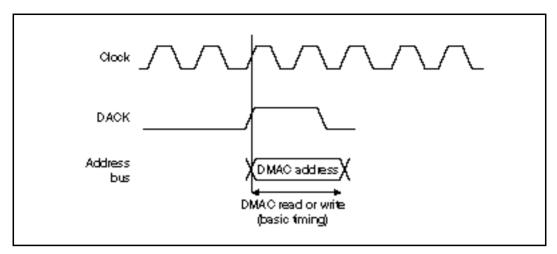

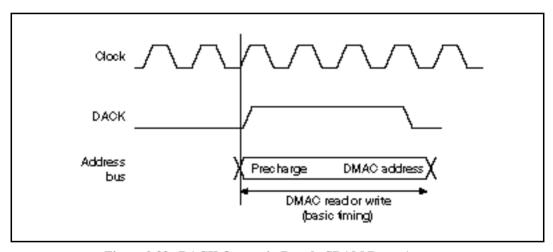

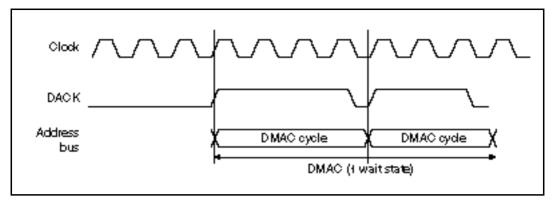

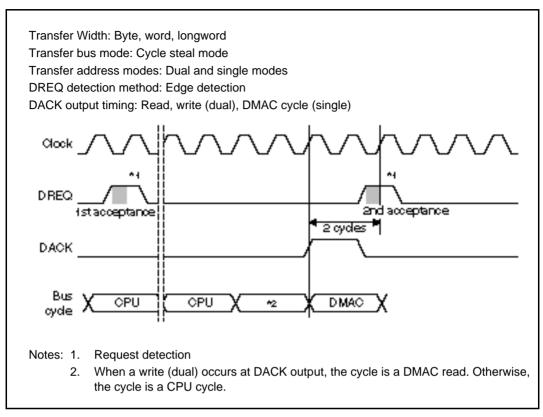

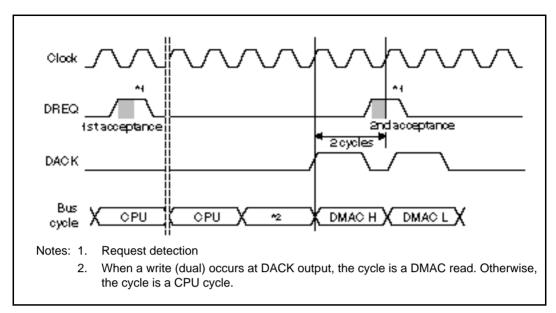

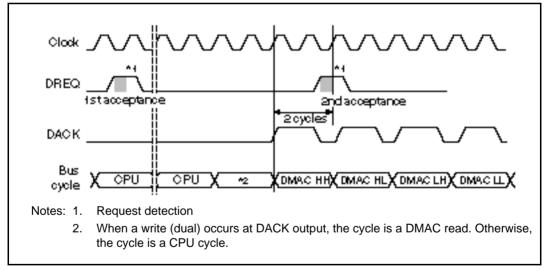

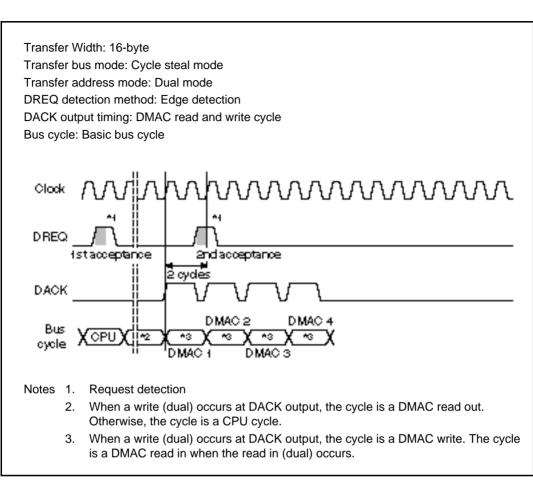

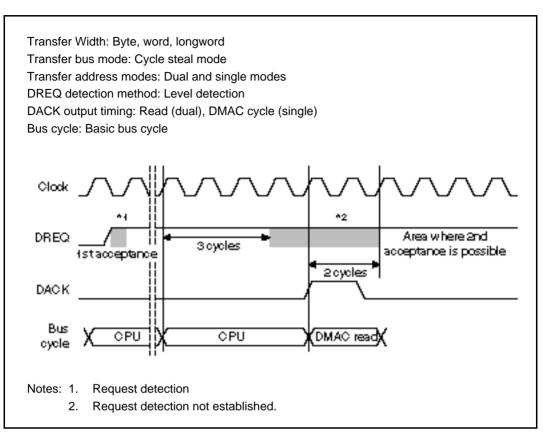

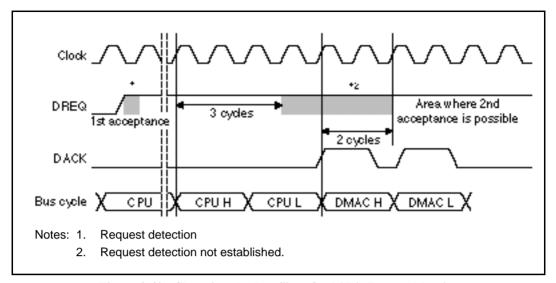

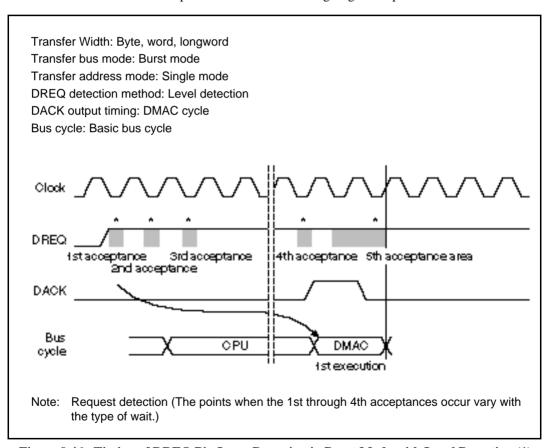

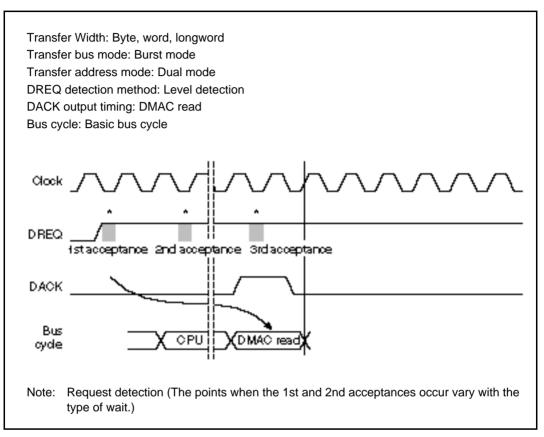

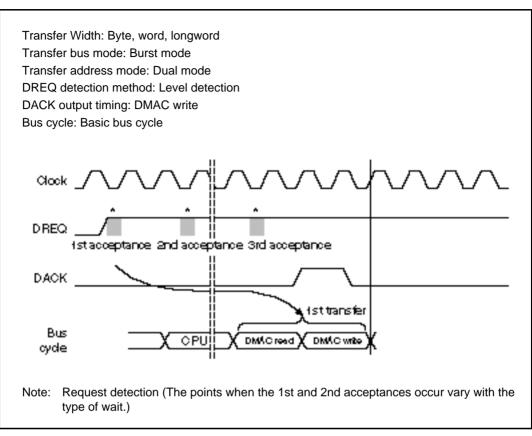

|      | 9.3.6   | DMA Transfer Request Acknowledge Signal Output Timing    | 249 |

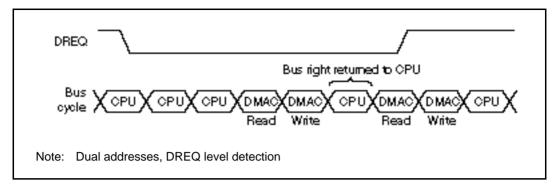

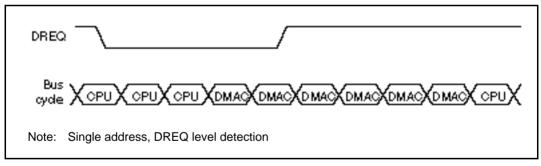

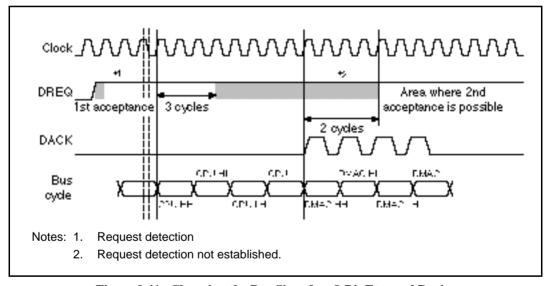

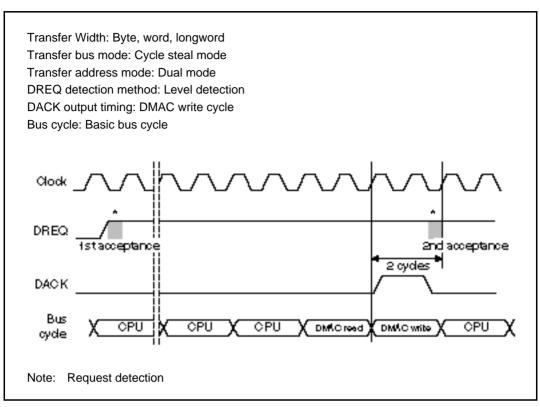

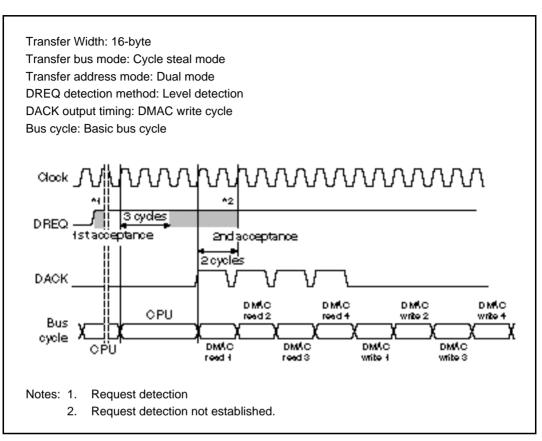

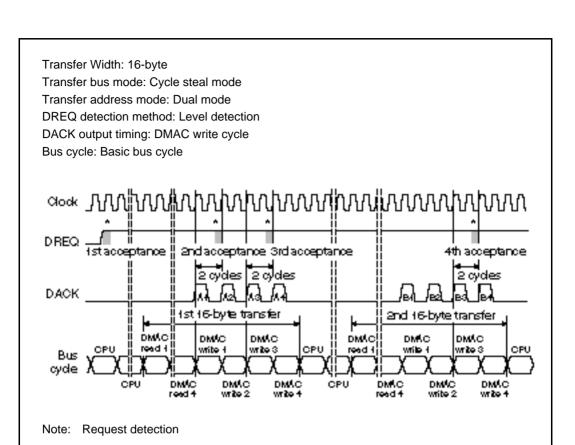

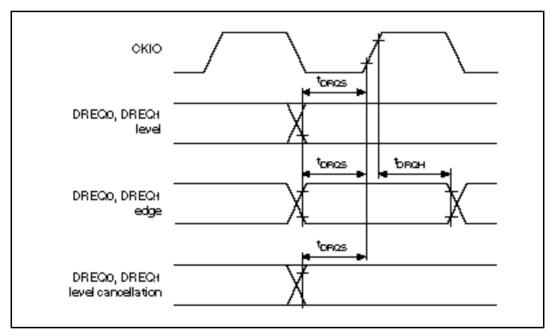

|      | 9.3.7   | DREQ Pin Input Detection Timing                          | 260 |

|      | 9.3.8   | DMA Transfer-End                                         | 272 |

| 9.4  | Examp   | les of Use                                               | 274 |

|      | 9.4.1   | DMA Transfer Between On-Chip SCI and External Memory     | 274 |

| 9.5  | Notes   |                                                          | 274 |

|      |         |                                                          |     |

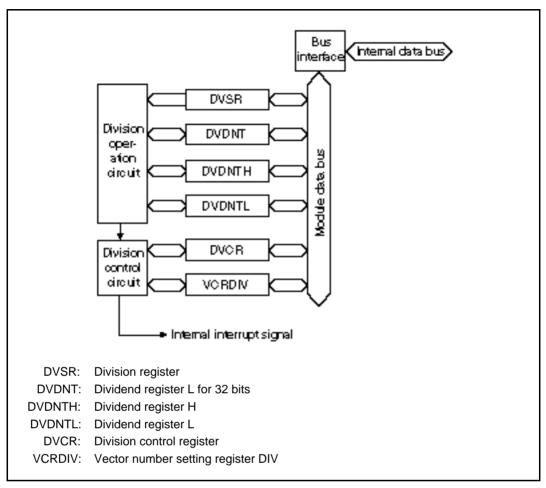

| Sect | ion 10  | Division Unit                                            | 277 |

| 10.1 | Overvi  | ew                                                       | 277 |

|      | 10.1.1  | Features                                                 | 277 |

|      | 10.1.2  | Block Diagram                                            | 277 |

|      | 10.1.3  | Register Configuration.                                  | 278 |

| 10.2 | Descrip | otion of Registers                                       | 279 |

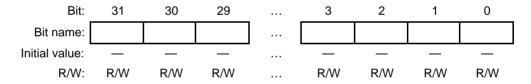

|      | 10.2.1  | Divisor Register (DVSR)                                  | 279 |

|      | 10.2.2  | Dividend Register L for 32-Bit division (DVDNT)          | 279 |

|      | 10.2.3  | Division Control Register (DVCR)                         | 280 |

|      |         | Vector Number Setting Register (VCRDIV)                  |     |

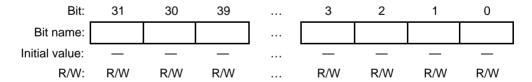

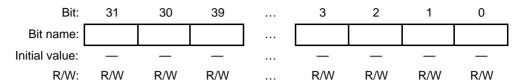

|      |         | Dividend Register H (DVDNTH)                             |     |

|      |         | Dividend Register L (DVDNTL)                             |     |

| 10.3 |         | on                                                       |     |

|      | -       | 64 Bit/32 Bit Operations                                 |     |

|      |         | 32 Bit/32 Bit Operations                                 |     |

|      |         | Handling of Overflows                                    |     |

| 10.4 |         | on Use                                                   |     |

|      |         | Access                                                   |     |

|      |         | Overflow Flag                                            |     |

|      |         |                                                          |     |

| Sect | ion 11  | 16-Bit Free-Running Timer                                |     |

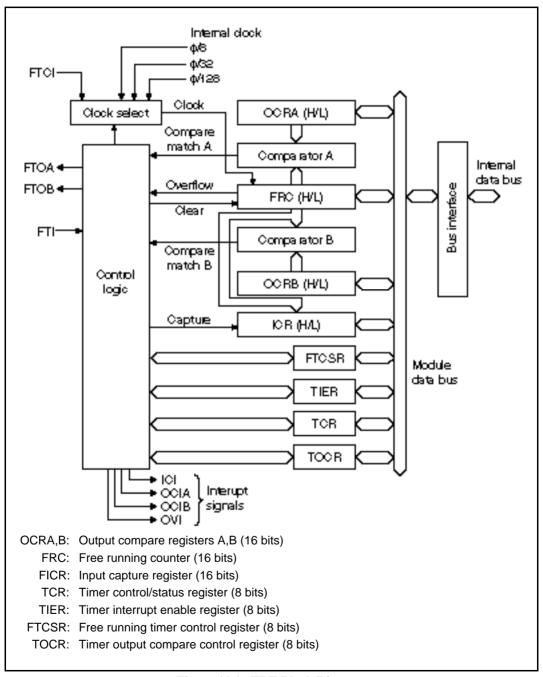

| 11.1 | Overvi  | ew                                                       | 285 |

|      | 11.1.1  | Features                                                 | 285 |

|      |         | Block Diagram                                            |     |

|      | 11.1.3  | Pin Configuration                                        | 287 |

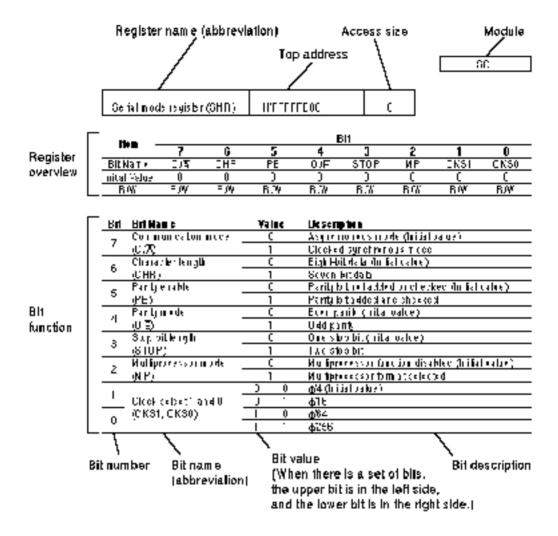

|       | 11.1.4                                                                                                                                                           | Register Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 287                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 11.2  | Registe                                                                                                                                                          | r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 288                                                                                            |

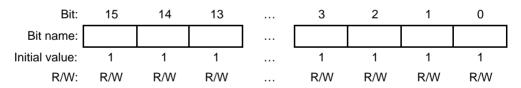

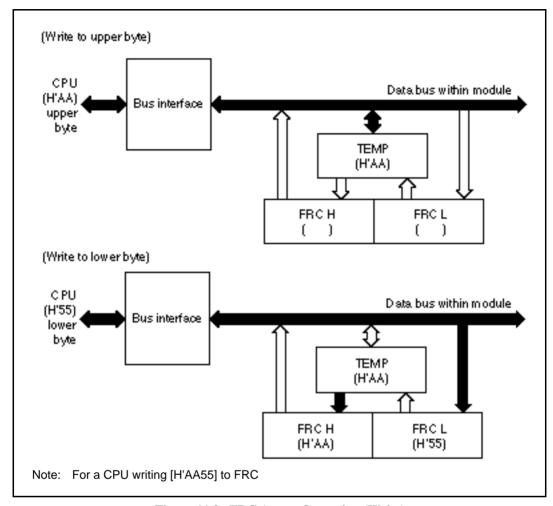

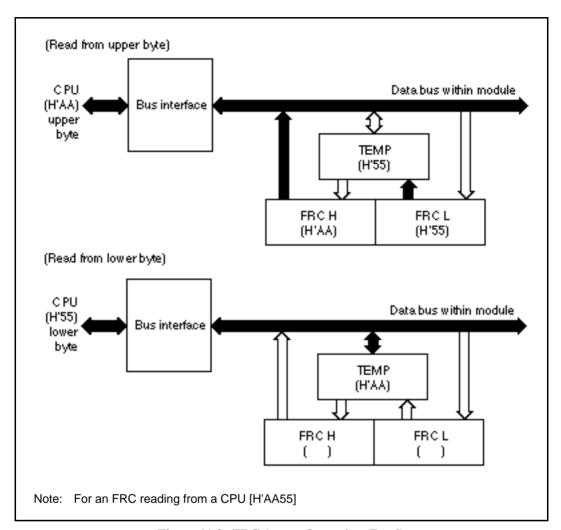

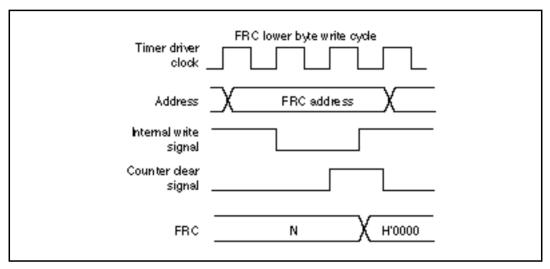

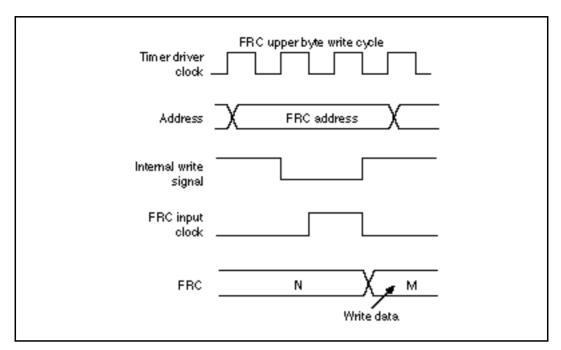

|       | 11.2.1                                                                                                                                                           | Free-Running Counter (FRC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 288                                                                                            |

|       | 11.2.2                                                                                                                                                           | Output Compare Registers A and B (OCRA and OCRB)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 288                                                                                            |

|       | 11.2.3                                                                                                                                                           | Input Capture Register (ICR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 289                                                                                            |

|       | 11.2.4                                                                                                                                                           | Timer Interrupt Enable Register (TIER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 289                                                                                            |

|       | 11.2.5                                                                                                                                                           | Free-Running Timer Control/Status Register (FTCSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 290                                                                                            |

|       | 11.2.6                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

|       | 11.2.7                                                                                                                                                           | Timer Output Compare Control Register (TOCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 293                                                                                            |

| 11.3  |                                                                                                                                                                  | terface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| 11.4  | Operati                                                                                                                                                          | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 298                                                                                            |

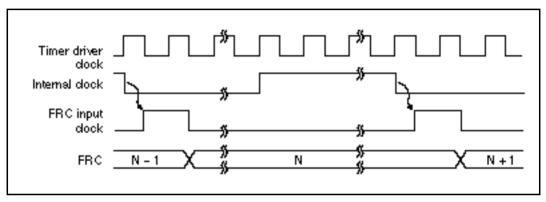

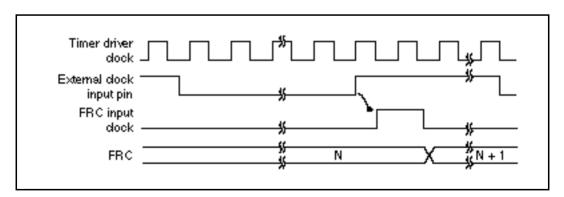

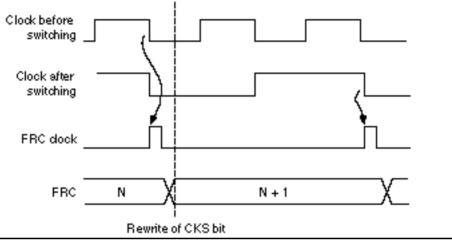

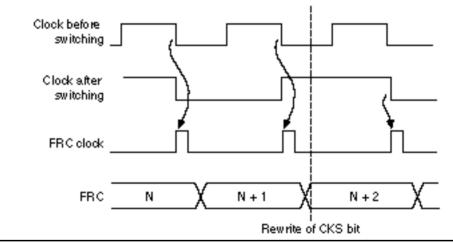

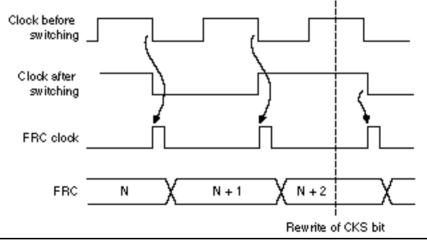

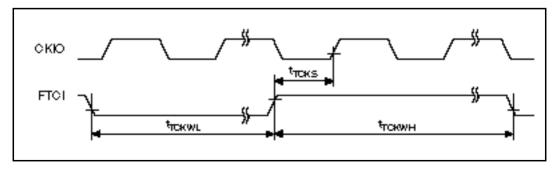

|       | 11.4.1                                                                                                                                                           | FRC Count Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 298                                                                                            |

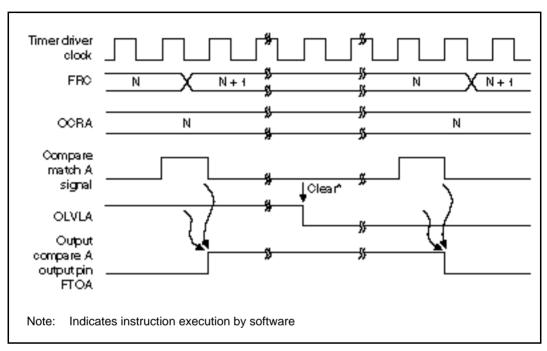

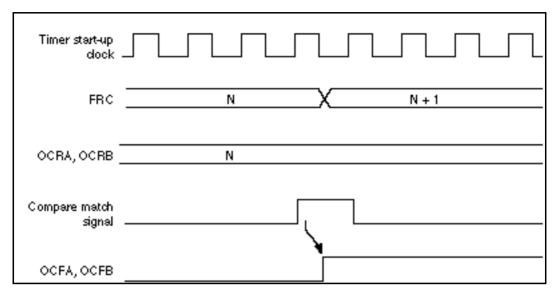

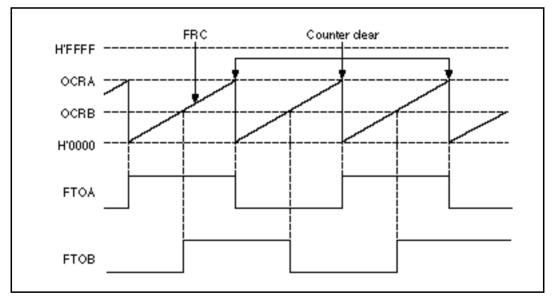

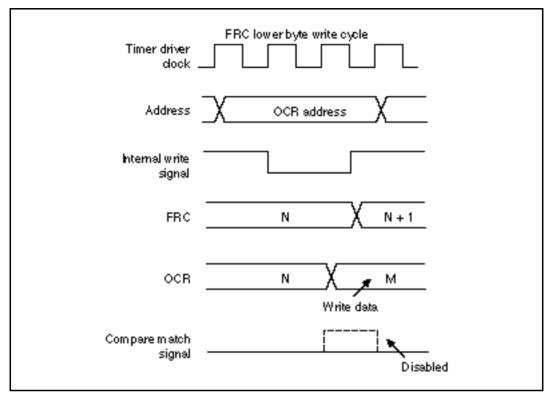

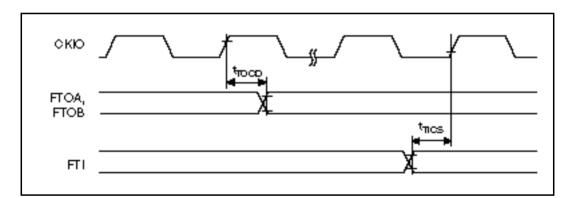

|       | 11.4.2                                                                                                                                                           | Output Timing for Output Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 299                                                                                            |

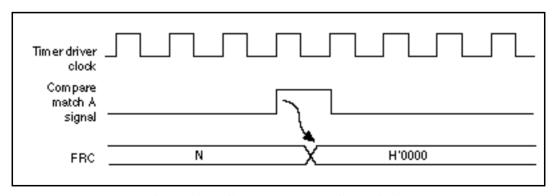

|       | 11.4.3                                                                                                                                                           | FRC Clear Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 299                                                                                            |

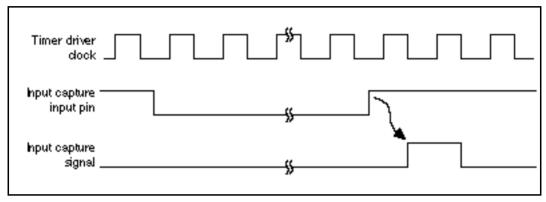

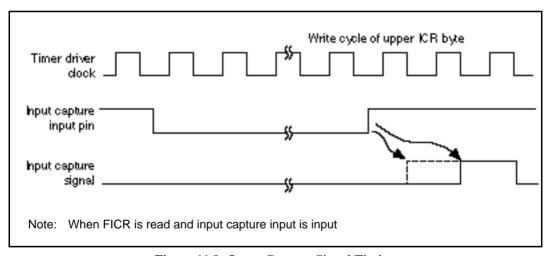

|       | 11.4.4                                                                                                                                                           | Input Capture Input Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 300                                                                                            |

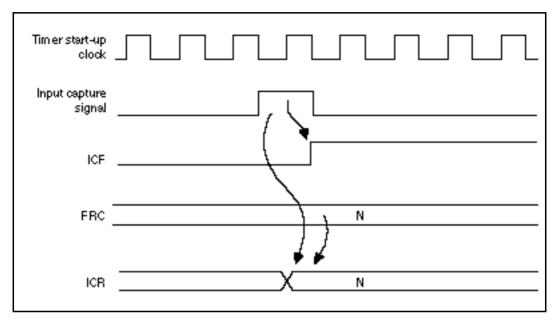

|       | 11.4.5                                                                                                                                                           | Input Capture Flag (ICF) Set Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 301                                                                                            |

|       | 11.4.6                                                                                                                                                           | Output Compare Flag (OCFA, OCFB) Set Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 301                                                                                            |

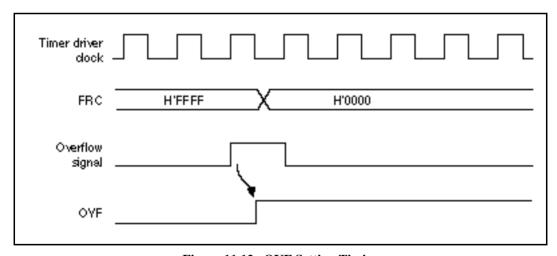

|       | 11.4.7                                                                                                                                                           | Timer Overflow Flag (OVF) Set Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 302                                                                                            |

| 11.5  | Interruj                                                                                                                                                         | ot Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 303                                                                                            |

| 11.6  | Examp                                                                                                                                                            | le of Using the FRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 303                                                                                            |

| 11.7  | Notes o                                                                                                                                                          | on Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 304                                                                                            |

|       |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

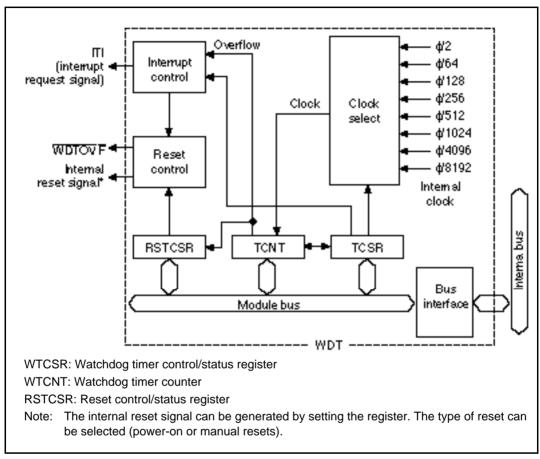

| Secti |                                                                                                                                                                  | Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 309                                                                                            |

| 12.1  |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| 12.1  |                                                                                                                                                                  | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

| 12.1  | 12.1.1                                                                                                                                                           | Features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 309                                                                                            |

| 12.1  | 12.1.1                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 309                                                                                            |

| 12.1  | 12.1.1<br>12.1.2<br>12.1.3                                                                                                                                       | Features.  Block Diagram.  Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 309<br>310<br>310                                                                              |

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4                                                                                                                             | Features Block Diagram Pin Configuration Register Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                          | 309<br>310<br>310<br>311                                                                       |

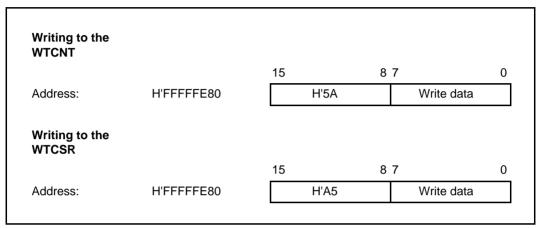

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe                                                                                                                  | Features.  Block Diagram.  Pin Configuration  Register Configuration  r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                     | 309<br>310<br>310<br>311<br>311                                                                |

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Register<br>12.2.1                                                                                                       | Features Block Diagram Pin Configuration Register Configuration r Descriptions Watchdog Timer Counter (WTCNT)                                                                                                                                                                                                                                                                                                                                                                                            | 309<br>310<br>310<br>311<br>311<br>311                                                         |

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Register<br>12.2.1<br>12.2.2                                                                                             | Features.  Block Diagram.  Pin Configuration.  Register Configuration.  r Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).                                                                                                                                                                                                                                                                                                                                | 309<br>310<br>310<br>311<br>311<br>311<br>312                                                  |

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Register<br>12.2.1<br>12.2.2<br>12.2.3                                                                                   | Features.  Block Diagram.  Pin Configuration.  Register Configuration.  The Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR).                                                                                                                                                                                                                                                                                     | 309<br>310<br>310<br>311<br>311<br>312<br>313                                                  |

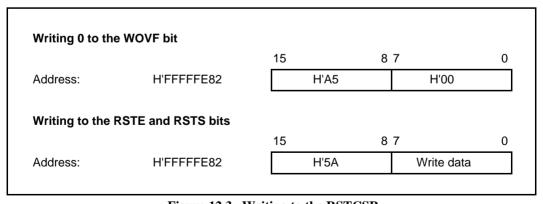

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Register<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4                                                                         | Features.  Block Diagram.  Pin Configuration.  Register Configuration.  r Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.                                                                                                                                                                                                                                                                      | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314                                           |

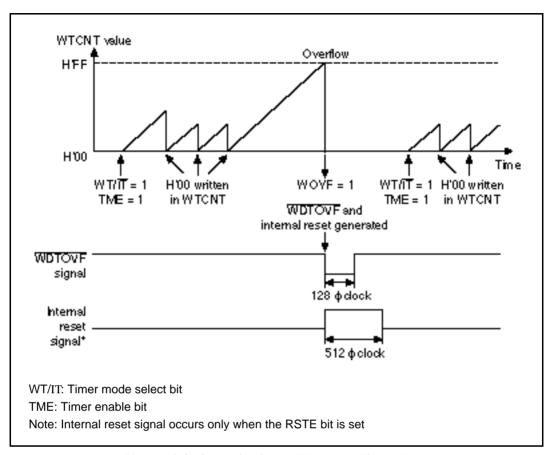

|       | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati                                                               | Features Block Diagram Pin Configuration Register Configuration r Descriptions Watchdog Timer Counter (WTCNT) Watchdog Timer Control/Status Register (WTCSR) Reset Control/Status Register (RSTCSR) Register Access on                                                                                                                                                                                                                                                                                   | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314<br>316                                    |

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati                                                               | Features.  Block Diagram.  Pin Configuration.  Register Configuration.  r Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.                                                                                                                                                                                                                                                                      | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314<br>316                                    |

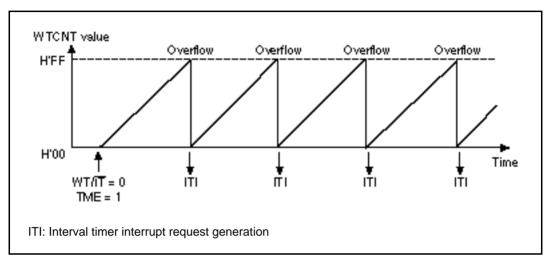

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati                                                               | Features.  Block Diagram.  Pin Configuration.  Register Configuration  r Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.  on.  Operation in the Watchdog Timer Mode.  Operation in the Interval Timer Mode.                                                                                                                                                                                    | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314<br>316<br>316<br>318                      |

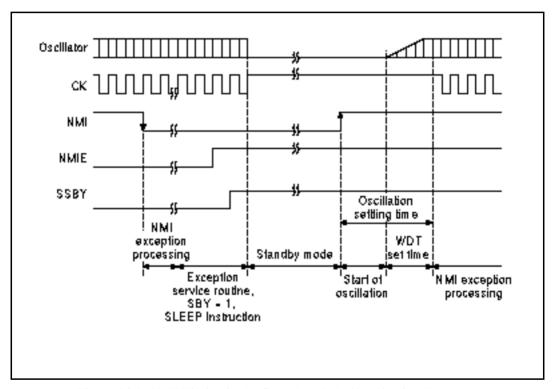

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Register<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operation 12.3.1                                                     | Features Block Diagram Pin Configuration Register Configuration r Descriptions Watchdog Timer Counter (WTCNT) Watchdog Timer Control/Status Register (WTCSR) Reset Control/Status Register (RSTCSR) Register Access On Operation in the Watchdog Timer Mode Operation in the Interval Timer Mode Operation in the Standby Mode                                                                                                                                                                           | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314<br>316<br>316<br>318                      |

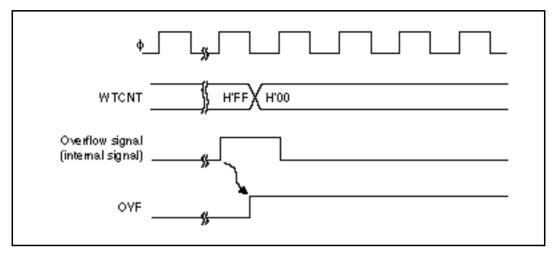

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati<br>12.3.1<br>12.3.2                                           | Features.  Block Diagram.  Pin Configuration.  Register Configuration  r Descriptions.  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.  on.  Operation in the Watchdog Timer Mode.  Operation in the Interval Timer Mode.  Operation in the Standby Mode.  Timing of Setting the Overflow Flag (OVF)                                                                                                         | 309<br>310<br>311<br>311<br>312<br>313<br>314<br>316<br>316<br>318<br>318<br>319               |

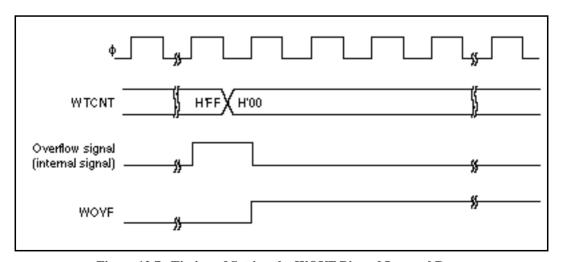

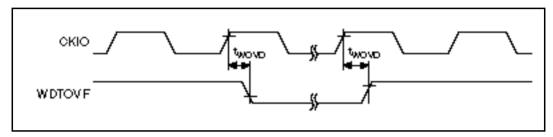

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5             | Features Block Diagram Pin Configuration Register Configuration  The Descriptions Watchdog Timer Counter (WTCNT) Watchdog Timer Control/Status Register (WTCSR) Reset Control/Status Register (RSTCSR) Register Access On Operation in the Watchdog Timer Mode Operation in the Interval Timer Mode Operation in the Standby Mode Timing of Setting the Overflow Flag (OVF) Timing of Setting the Watchdog Timer Overflow Flag (WOVF)                                                                    | 309<br>310<br>311<br>311<br>311<br>312<br>313<br>314<br>316<br>318<br>319<br>319               |

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>Notes of | Features.  Block Diagram.  Pin Configuration  Register Configuration  r Descriptions  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.  on.  Operation in the Watchdog Timer Mode.  Operation in the Interval Timer Mode.  Operation in the Standby Mode.  Timing of Setting the Overflow Flag (OVF)  Timing of Setting the Watchdog Timer Overflow Flag (WOVF).  on Use.                                      | 309<br>310<br>311<br>311<br>312<br>313<br>314<br>316<br>318<br>319<br>319<br>320               |

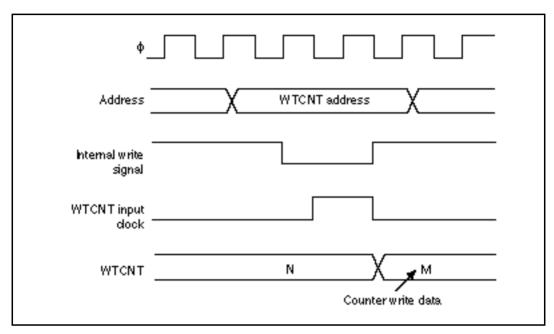

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>Notes of | Features.  Block Diagram.  Pin Configuration  Register Configuration  r Descriptions  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR)  Reset Control/Status Register (RSTCSR)  Register Access.  on.  Operation in the Watchdog Timer Mode.  Operation in the Interval Timer Mode.  Operation in the Standby Mode.  Timing of Setting the Overflow Flag (OVF)  Timing of Setting the Watchdog Timer Overflow Flag (WOVF).  on Use.  WTCNT Write and Increment Contention | 309<br>310<br>311<br>311<br>312<br>313<br>314<br>316<br>318<br>319<br>319<br>320<br>320        |

| 12.2  | 12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>Registe<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>Operati<br>12.3.1<br>12.3.2<br>12.3.3<br>12.3.4<br>12.3.5<br>Notes of | Features.  Block Diagram.  Pin Configuration  Register Configuration  r Descriptions  Watchdog Timer Counter (WTCNT).  Watchdog Timer Control/Status Register (WTCSR).  Reset Control/Status Register (RSTCSR)  Register Access.  on.  Operation in the Watchdog Timer Mode.  Operation in the Interval Timer Mode.  Operation in the Standby Mode.  Timing of Setting the Overflow Flag (OVF)  Timing of Setting the Watchdog Timer Overflow Flag (WOVF).  on Use.                                      | 309<br>310<br>311<br>311<br>312<br>313<br>314<br>316<br>318<br>319<br>319<br>320<br>320<br>320 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 321                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

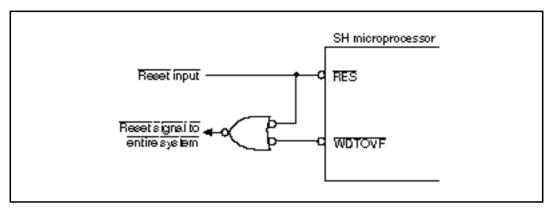

| eset With the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 321                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   |

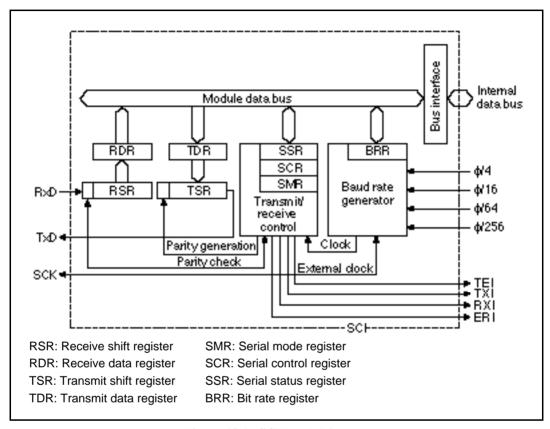

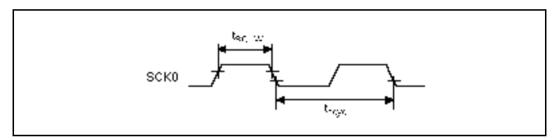

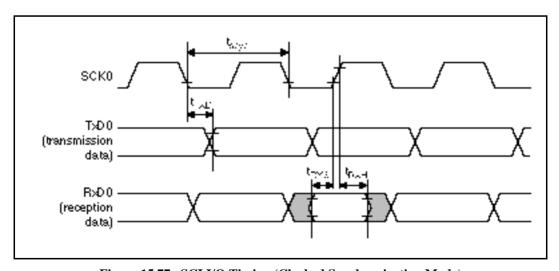

| ommunication Interface 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                   |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 323                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 323                                                                                                                                                                                                                                                                               |

| gram3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 324                                                                                                                                                                                                                                                                               |